Blocs analogiques élémentaires en technologie CMOS

option EC - 2001/2002

Blocs analogiques élémentaires

en technologie CMOS

option EC - 2001/2002

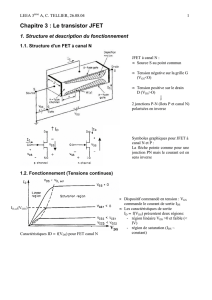

Transistor MOS

VDS

IDS

VDS-sat

()

DSTGSoxDS VVV

L

W

CI −µ=

()()()

DSsatDS

2

TGSoxDS VV1VV

L

W

C

2

1

I−λ+−µ=

()

2

V

VVV

L

W

CI 2

DS

DSTGSoxDS −−µ=

D

S

G

IDS

VDS

VGS

VDS-sat=VGS-VT

option EC - 2001/2002

•schéma équivalent "petits signaux" pour la zone

active (small-signal model)

gmvgs rds

GD

S

C

gd

Csb

Cgs Cdb

()

T

GS

DS

DSoxTGSoxm VV I2

I

L

W

C2VV

L

W

Cg −

=µ=−µ=

()

DS

2

TGS

ox

ds

ds

IVV

L

W

2

C

g

r

1

λ≅−

µ

λ==

Transistor MOS

()()()

DSsatDS

2

TGSoxDS VV1VV

L

W

C

2

1

I−λ+−µ=

option EC - 2001/2002

•schéma équivalent "petits signaux" pour la zone

active (small-signal model)

Transistor MOS

()()()

DSsatDS

2

TGSoxDS VV1VV

L

W

C

2

1

I−λ+−µ=

DS

ds

I

r

1

λ

≅

résistance de sortie :

()

biTGSDS

A

0Si

VVVVL2 qN

2

+−−

εε

=λ

ordres de grandeur :

nMOS : 4 10-7 m/√V, pMOS : 10 -8 m/

√

0,9V

option EC - 2001/2002

•effet du substrat :

lorsque le substrat n'est pas au même potentiel que la source, la

tension de seuil du transistor est modifiée

(pour un transistor nMOS, la tension de seuil augmente lorsque

la tension VSB augmente (source to bulk))

Transistor MOS

(

)

ox

0A

FFSB0tntn

CKqN2

avec

22VVV

ε

=γ

Φ−Φ+γ+= gmvgs rds

GD

S

Cgd

Csb

Cgs C

db

B

gsvbs

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

1

/

49

100%