Les mémoires relèvent le défi de l`« infoplosion » dans

28 / L’EMBARQUÉ / N°7 / 2014

A P P L I C A T I O N

Stockage

Les mémoires relèvent

le défi de l’« infoplosion » dans

les systèmes embarqués

L

es données qui sont créées,

enregistrées et partagées

aujourd’hui à un rythme phé-

noménal dans l’économie

numérique génèrent une véritable

« explosion d’information », que l’on

pourrait nommer en utilisant le néo-

logisme « infoplosion » et qui menace

de submerger les entreprises et les

consommateurs. La société d’études

de marché IDC prévoit ainsi que la

capacité de stockage brute disponible

dans le monde passera de 2 596 Eo

(exaoctets) en 2012 à 7 235 Zo (zet-

taoctets) en 2017. Pour mettre ce

nombre en perspective, 1 Eo est égal

à 1.000.000.000.000.000.000 octets

ou 1018 octets (et 1 Zo égale

1021 octets). Concrètement, 1 Eo est

équivalent à la mémoire disponible

sur 31 millions d’iPads dotés chacun

de 32 Go de mémoire.

L’essor des terminaux intelligents tels

que les tablettes, les smartphones, les

montres intelligentes, les réfrigéra-

teurs ou les compteurs communi-

cants fait rapidement croître la

demande envers des technologies de

mémoire flash NAND capables

d’être embarquées dans des espaces

restreints. En outre, les périphériques

de stockage à base de flash NAND,

comme les disques SSD (Solid State

Disk), ou disques à semi-conduc-

teurs, ou les clés USB remplacent

désormais de plus en plus les disques

durs traditionnels et les médias

optiques, notamment lorsque la

vitesse d’accès aux données est cri-

tique. Dans de nombreux systèmes

informatiques du type Big Data ou

Cloud, les SSD sont tout en haut des

systèmes de stockage intégrant à la

fois des SSD et des HDD (Hard Disk

Drive) ou disques durs magnétiques.

Corollaire de la croissance de la

demande en technologie NAND, le

coût par gigaoctet a diminué, stimu-

lant ainsi davantage la demande.

Une des raisons principales de cette

évolution est que la densité de don-

nées stockables sur une puce flash

NAND de dimension donnée n’a fait

qu’augmenter. Les flash NAND ont

en effet toujours été en pointe et

pionnière dans la mise en œuvre

industrielle des procédés de lithogra-

phie utilisés par l’industrie électro-

nique. Conséquence, à l’heure

actuelle, les mémoires NAND sont

parmi les circuits intégrés produits en

masse les plus denses.

Quelques chiffres : depuis l’introduc-

tion des NAND en 1984, la taille de

la cellule élémentaire est passée de

700 nm à 19 nm et, avec l’introduc-

tion de nouvelles technologies au

niveau des cellules, la densité de bits

des NAND a été multipliée par plus

de 2 000 ! Parallèlement à cette aug-

mentation de densité, on a pu obser-

ver une formidable réduction du prix

par gigaoctet, qui a diminué encore

plus rapidement que la densité de

bits n’a augmenté. En plus des avan-

tages de coût résultant de la minia-

turisation lithographique, l’introduc-

tion de traitements automatisés plus

efficaces et de wafers (plaquettes de

silicium) de plus grand diamètre a

permis aux NAND de devenir le sup-

port de stockage favori de nom-

breuses applications.

Les mémoires NAND

face à de nombreux défis

L’un des principaux défis à relever

pour ceux qui veulent utiliser les tout

derniers types de NAND brutes dans

leurs projets tient au fait que ces nou-

velles technologies ont besoin de

moteurs ECC (Error Correction Code,

ou code de correction d’erreur) plus

puissants intégrés aux contrôleurs. Et

cette course est devenue permanente

puisqu’en général les contrôleurs ont

du mal à tenir la cadence. Comme

L’industrie des mémoires numériques vit une période de changement spectaculaire avec

une utilisation croissante des technologies flash NAND pour la mémoire embarquée. Depuis

son invention en 1984 par Toshiba, leur capacité a considérablement augmenté, tandis que

le coût par gigaoctet a fondu. Pourtant il reste de nombreux défis à relever. Revue de détail.

Axel

Stoermann,

directeur

général

marketing OEM

et Applications

mémoire,

Toshiba

Electronics

Europe.

AUTEUR

● Les puces NAND gravés en 19 nm sont dotées d’une capacité qui

va de 60 Go à 512 Go, sous différents formats. On les retrouve dans

les disques durs SSD 2,5 pouces, mSATA et M2 (simple et double face).

Les versions destinées aux entreprises disposent d’une option

d’autochiffrement conforme aux spécifications du Trusted Computing Group.

L’EMBARQUÉ / N°7 / 2014 / 29

Stockage

A P P L I C A T I O N

les blocs de mémoire NAND se

dégradent et s’usent, on doit fixer

une limite haute au nombre d’écri-

tures de chaque emplacement

mémoire. Des algorithmes de « nive-

lage d’usure » doivent aussi être inté-

grés aux contrôleurs NAND pour

assurer une utilisation équitable de

tous les emplacements mémoire.

Pour ceux qui souhaitent réduire le

nombre de composants système et

ne pas se préoccuper d’architecture

contrôleur, les NAND e-MMC offrent

une alternative intéressante, qui

intègre à la fois la puce mémoire

flash et le contrôleur NAND dans un

même module. Ces dispositifs sont

typiquement utilisés dans les cartes

mémoire et les clés USB rapides, et

sont conformes aux normes JEDEC.

Les contrôleurs embarqués exécutent

des opérations de contrôle comme

la correction d’erreurs, le nivelage

d’usure et la gestion des blocs défec-

tueux pour garantir le bon fonction-

nement de la mémoire NAND.

L’un des défis associés à la migration

vers de plus petits éléments de stoc-

kage est le besoin de contrôle ECC

plus complexe, et donc de proces-

seurs hôtes de plus en plus puissants.

Pour des SLC (Single Level Cell, ou

cellule simple niveau) produite en

technologie 43 nm, 1 bit d’ECC par

tranche de 512 octets est nécessaire.

Un chiffre qui monte à 8 bits par

tranche de 512 octets pour des SLC

en 24 nm.

Pour de nombreuses applications

existantes qui utilisent de la mémoire

NAND SLC, comme les produits

industriels, les processeurs de

communication ou les systèmes

automobiles, des ECC à 1 bit sont

implémentés dans le logiciel

hôte sans impact significatif sur

la performance des applications.

Cependant, migrer vers des

mémoires de pointe nécessitant

des ECC à 4, 8, voire 24 bits, aug-

mente sensiblement la charge du

processeur, réduisant ainsi ses

performances. Afin d’éviter cet

écueil, les puces NAND à cor-

rection d’erreurs embarquée sont

désormais préférées. A l’instar

des modèles BENAND de

Toshiba qui soulagent le proces-

seur hôte de la tâche de correc-

tion d’erreurs sans nécessiter de

contrôleur matériel supplémen-

taire. Ces BENAND utilisent la

même interface que les NAND

classiques et offrent ainsi une com-

patibilité avec les mémoires flash

NAND SLC au niveau commandes,

fonctionnement général, condition-

nement et brochage.

Esquisses des mémoires

du futur

Si la technologie existe pour produire

des NAND à cellules élémentaires

encore plus petites, cette diminution

de la taille va à l’encontre de leur

endurance et de leur fiabilité. Pour

surmonter cela, des cellules NAND

capables de stocker plusieurs bits

mémoire ont été développées. Car si

les cellules SLC ne peuvent stocker

que 1 bit par cellule, les MLC (Mul-

ti-Level Cell, ou cellule multini-

veaux), de leur côté, peuvent en stoc-

ker 2, tandis que les TLC (Triple level

Cell, ou cellule triple-niveau) peuvent

stocker 3 bits par cellule. Cependant,

l’endurance à l’écriture et à l’efface-

ment est impactée par de telles

approches. Les SLC peuvent ainsi

supporter environ 100 000 cycles,

contre 5 000 cycles pour les MLC, et

seulement 1 000 cycles pour les TLC.

Aujourd’hui la situation est la sui-

vante : les NAND SLC et MLC sont

désormais utilisées couramment dans

les disques d’entreprise qui doivent

résister à de fréquents cycles d’écri-

ture ou d’effacement tandis que les

NAND MLC et TLC se rencontrent

dans les SSD grand public, là où la

vitesse de lecture et le prix par

gigaoctet sont devenus les facteurs les

plus influents dans les profils d’achat.

Une façon d’éviter ces problèmes

liés à l’augmentation du nombre de

bits par cellule est de considérer de

nouvelles technologies NAND.

Parmi celles-ci, la plus proche de la

phase de production en série est la

NAND 3D. Il s’agit ici d’empiler plu-

sieurs couches de NAND l’une sur

l’autre, afin d’augmenter la capacité

sans devoir rétrécir les dimensions

horizontales.

La mémoire RAM magnétorésistive

(MRAM) est une autre technologie

prometteuse. Il s’agit d’une forme de

mémoire non volatile extrêmement

rapide, offrant une endurance prati-

quement illimitée à l’écriture et à l’ef-

facement. De ce fait, la technologie

MRAM a le potentiel de changer la

manière dont tous les appareils élec-

troniques utilisent la mémoire

flash NAND. Aujourd’hui, on uti-

lise en effet la flash NAND comme

un disque dur : les données sont

copiées au démarrage depuis la

flash NAND vers la DRAM

(mémoire vive dynamique), puis

le code est exécuté à partir de

cette DRAM. Avec la MRAM, plus

besoin de mettre en œuvre cette

approche dite de « shadowing »

(recopie des données de la RAM

vers la DRAM). Les données sont

en effet déjà prêtes dès la mise

sous tension, et la vitesse de lec-

ture est quasiment la même que

celle de la DRAM. Ce qui offre

l’avantage supplémentaire de

nécessiter moins d’endurance de

la flash NAND, qui peut alors ser-

vir à l’archivage des données à

plus long terme. n

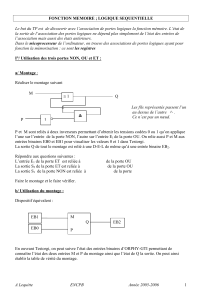

Cost

4 x nm 3 x nm 2 x nm

ECC

4 x nm 3 x nm 2 x nm

1 bit

4 bits

8 bits

TENDANCES DES FLASH NAND

On voit ici les avantages de la réduction du coût

des technologies de mémoires avancées par rapport

au surcroît de complexité des codes de correction

d’erreurs.

● Les modèles BENAND de Toshiba soulagent le processeur

hôte de la tâche de correction d’erreurs, sans nécessiter de

contrôleur matériel supplémentaire. Ces mémoires utilisent la

même interface que les NAND classiques et offrent ainsi une

compatibilité ascendante avec les mémoires flash NAND SLC

au niveau commandes, fonctionnement général,

conditionnement et brochage.

1

/

2

100%