Dr Dhafer MEZGHANI

Examen Session MAI 2021

Section

Epreuve

Pages

Durée

Date

LPHE3

Electronique Numérique

6

1H30

17Mai 2022

Documents autorisés : Oui Non Calculatrice autorisée : Oui Non

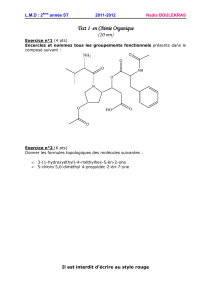

Exercice 1 (8 points) :

Dans une usine de fabrication de boites on effectue un contrôle de qualité selon 3 critères :

- Poids P, (0 incorrect, 1 correct)

- Diamètre D, (0 incorrect, 1 correct)

- Hauteur H, (0 incorrect, 1 correct)

Cela permet de classer les boites en 3 catégories :

- Qualité A=1 : Si Le poids P et une de deux dimensions au moins sont corrects,

- Qualité B=1 : Si Le poids P seul est correct ou une de deux dimensions au moins est correcte,

- Qualité C=1 : Si Le poids P et les deux dimensions sont incorrects.

1) (3 pts) Compléter la table de vérité du système avec les entrées sont P, D et H et les

variables de sortie sont A, B et C,

P

D

H

A

B

C

2) (3 pts) Donner les expressions simplifiées des sorties A, B et C en utilisant le tableau de

Karnaugh.

République Tunisienne

Ministère de l’Enseignement Supérieur

et de la Recherche Scientifique

Année Universitaire

2016-2017

Dr Dhafer MEZGHANI

A= ………………………………………………..

B=…………………………………………………

C=…………………………………………………

3) (2 pts) Donner le circuit logique avec les portes logiques de base.

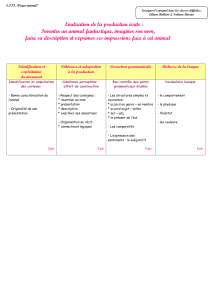

Exercice 2 (6 points) :

On donne le circuit logique suivant

Dr Dhafer MEZGHANI

1/(1 pt) Donner l’équation logique de la fonction F

F=…………………………………………………………………………………………………………………………..

2/ (2 pt) Déduire la première forme canonique de la fonction F

F=…………………………………………………………………………………………………………………………..

3/ (1.5 pts) Concevoir la fonction F avec un multiplexeur avec les signaux de contrôle ABC (A est le

bit le plus fort, C est le bit le plus faible)

4/ (1.5 pts) Concevoir la fonction F avec un décodeur 4 vers 16 et des porte(s) logique(s) (A est le bit

le plus fort, D est le bit le plus faible)

Dr Dhafer MEZGHANI

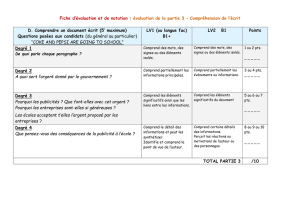

Exercice 3 (6 points) :

1/ (2 pts) On donne le circuit logique suivant d’un additionneur complet à 1 bit :

Compléter la table de vérité pour les deux fonctions S et C1 en fonction de A, B et C0

A

B

C0

S

C1

2/ (2 pts) en utilisant le symbole logique d’un additionneur complet à 1 bit ci-dessous, concevoir

schématiquement un additionneur parallèle à retenue propagée à 4 bits en utilisant des

additionneurs complets à 1 bit. Cet additionneur à 4 bits permet de faire l’opération addition entre A

=A3A2A1A0 et B=B3B2B1B0. La retenue initiale de cet additionneur est notée R0 et la retenue finale

est notée R4, le résultat sera S=S3S2S1S0.

Dr Dhafer MEZGHANI

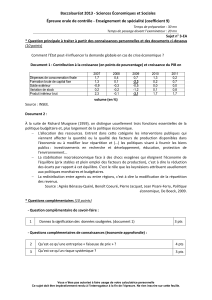

3/ (2 pts) le symbole logique d’un additionneur parallèle à retenue propagée à 4 bits est comme suit

On désire implémenter l’opération suivante : S=A-B = 5-2 = 3 sur le circuit additionneur/soustracteur

ci-dessous. Donner les 18 valeurs binaires marquées par « ? » pour satisfaire cette opération

arithmétique.

6

6

1

/

6

100%