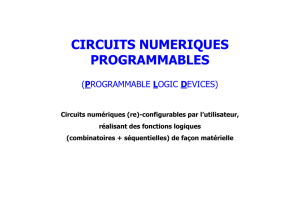

Logique Programmable: PLA, PAL, GAL, CPLD - Présentation

Telechargé par

BETOMBO Gillan

INF3500 : Conception et implémentation de systèmes numériques

http://creativecommons.org/licenses/by-nc-sa/2.5/ca/

Pierre Langlois

Logique programmable

Réseaux et circuits PLA, PAL, GAL et CPLD

INF3500 : Conception et implémentation de systèmes numériques

Sujets de ce thème

•Réseaux de logique programme PLA

•Circuit PAL

•Circuit GAL

•Circuits logiques programmables complexes CPLD

2

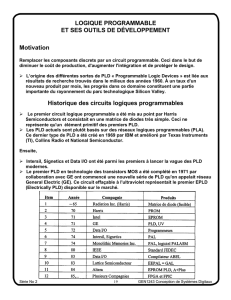

Technologies de circuits intégrés à application spécifique (ASIC)

Logique fixe Logique programmable

ASIC

sur mesure

Full-custom ASIC

ASIC à cellules normalisées

Cell-based ASIC

Réseau

pré-diffusé de portes

Gate Array

Mémoire

morte

Programmable Read Only Memory – PROM

Electrically Programmable ROM – EPROM

Erasable EPROM – EEPROM

Réseau

de logique programmable

Programmable Logic Array - PLA

Circuit

PAL

Programmable Array Logic™ - PAL

Circuit

GAL

Generic Array Logic™ - GAL

Circuit

logique programmable complexe

Complex Programmable Logic Device – CPLD

Réseau

prédiffusé pogaale pa l’utilisateu

Field-Programmable Gate Array – FPGA

INF3500 : Conception et implémentation de systèmes numériques

Réseaux de logiques programmable : PLA, PAL et GAL

•L’ipletatio de iuits logiues ave des

circuits SSI, MSI et LSI nécessite beaucoup de

travail pour choisir, disposer et relier les

composantes discrètes.

•Certaines fonctions logiques complexes peuvent

être remplacées par des PROM, mais une mémoire

est en général trop grande et pas assez flexible

pour bien convenir à la tâche.

•Les PLA (1970), et PAL (1978) étaient plus efficaces

que les PROM; ils pouvaient être programmés chez

le aufatuie ou ue fois pa l’utilisateu.

•Les GAL sont la version améliorée des PLA et PAL

et sot pogaales pa l’utilisateu.

3

INF3500 : Conception et implémentation de systèmes numériques

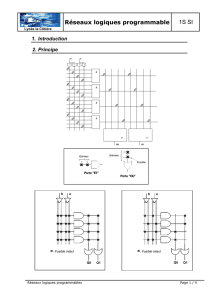

ROM vs PLA: pole d’effiait de la ROM

4

ROM 16 × 8 PLA à 4 entrées, 3 sorties et 6 termes

F0

A0

A1

A2

F1

F2

A3

décodeur 4:16

m7

m6

m5

m4

m3

m2

m1

m0

A2

A1

A0

A3

m15

m14

m13

m12

m11

m10

m9

m8

D7D6D5D4D3D2D1D0

INF3500 : Conception et implémentation de systèmes numériques

Réseaux de logiques programmables : PLA

•Un PLA (Programmable Logic Array) est similaire à

une ROM, mais il ne réalise pas tous les produits

de termes comme une ROM.

•Un PLA à n entrées et m sorties peut réaliser m

fonctions de n variables, en autant que chacune

requiert un nombre limité de produits des

variables en entrée.

•Un PLA est composé de deux réseaux

programmables, ET et OU. Le réseau ET

programmable est effectivement un décodeur

programmable incomplet.

5

•Chaue itesetio d’ue lige hoizotale et d’ue lige vetiale est pogaale.

•Seuls 6 termes (produits – ET logique) peuvent être réalisés à partir des quatre entrées et de leurs compléments.

•Seules trois fonctions de sortie peuvent être réalisées.

•Chaue fotio peut utilise ’ipote leuel des six tees pogas

F0

A0

A1

A2

F1

F2

A3

Exemple: PLA à 4 entrées, 3 sorties et 6 termes

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

1

/

17

100%