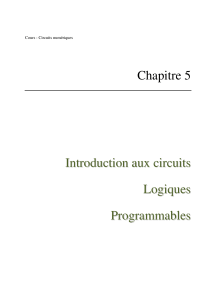

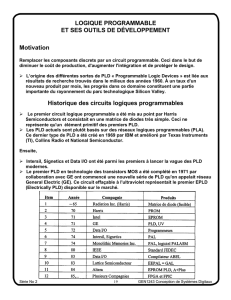

Réseaux logiques programmables

Réseaux logiques programmables Page 1 / 4

Lycée la Côtière

Réseaux logiques programmable

1S SI

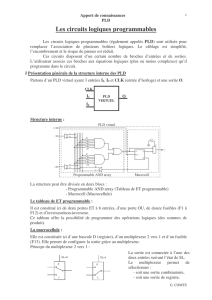

1. Introduction

2. Principe

a

b

1 1 1 1

&

&

&

&

Q0 Q1

>1 >1

Entrées

Porte "ET" Porte "OU"

Entrées

Fusible

a

b

Q0 Q1

: Fusible intact

ab

Q0 Q1

: Fusible intact

Réseaux logiques programmables Page 2 / 4

3. Différentes familles de PLD

TYPE Nombre de portes intégrées Matrice ET Matrice OU Effaçable

PROM 2 000 à 500 000 Fixe Programmable Non

PAL 10 à 100 Programmable Fixe Non

GAL 10 à 100 Programmable Fixe Electriquement

EPLD 100 à 3000 Programmable Fixe Aux U-V

FPLA 2000 à 3000 Programmable Programmable Electriquement

4. Les PAL (Programmable Array Logic)

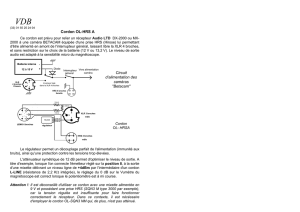

4.1. Structure

Porte trois états permettan

t

de déconnectée la broch

e

de la matrice "ET"

I/O

4.2. Référence

PAL (CE) XX AB YY C ZZ DEF

Type de boîtier

Vitesse

Consommation

Nombre de sorties

Structure de sortie

Nombre d’entrées

CE pour version CMOS

PAL

Lettre(s) Code(s) Structure de sortie

L Combinatoire active bas

H Combinatoire active haut

C Combinatoire complémentaire

R Registre synchrone (D)

RA Registre asynchrone

X Registre et OU exclusif

V Versatile

Réseaux logiques programmables Page 3 / 4

Exemple : PAL 16 L 8 H 15 PC

Type de boîtier : DIL plastique civile

Vitesse : 15 nS

Consommation : ½ puissance

Nombre de sorties : 8

Structure de sortie : Combinatoire active niveau Bas

Nombre d’entrées : 16

4.3. Exemples

Le PAL 16L8.

Ce type de circuit est uniquement constitué de logique combinatoire.

Il possède 20 broches agencées de la façon suivante :

- 10 broches configurables uniquement en entrée

- 2 broches configurables uniquement en sortie

- 6 broches configurables en entrée et en sortie

- 2 broches d’alimentation.

Le PAL 16R8.

Ce type de circuit est constitué de logique combinatoire et séquentielle.

Il possède 20 broches agencées de la façon suivante :

- 8 broches (n° 2 à 9) configurables uniquement en entrée

- 1 broche (n° 1) d’entrée d’horloge de l’ensemble des 8 bascules D

- 1 broche (n° 11) de validation des 8 sorties (output enable)

- 8 broches (n° 12 à 19) configurables en sortie et pouvant être réinjecter en entrée

- 2 broches d’alimentation (n° 10 et 20).

L’ensemble des sorties provient de portes 3 états inverseuses provenant elles-mêmes de

Réseaux logiques programmables Page 4 / 4

5. Les GAL (Generic Array Logic).

L’inconvénient majeur des PALs est qu’ils ne sont programmables qu’une seule fois.

Les GALs ou « Réseau logique Générique » peuvent être reprogrammés à volonté : on a remplacé les

fusibles irréversibles des PALs par des transistors MOS FET pouvant être régénérés

On peut aussi noter que dans leur structure interne les GALs sont constitués de transistor CMOS alors

que les PALs classiques sont constitués de transistors bipolaires. La consommation des GALs est donc beaucoup

plus faible.

Certains constructeurs fabriquent ce type de produit en les appelant « PAL CMOS ».

Par soucis de remplacer les PALs, la plupart de ses GALs de macro-cellules programmables (OLMC :

Output Logical Macro Cellule) permettant d’émuler n’importe quel PAL. Ces structures de sortie sont donc du type

« Versatile » (V).

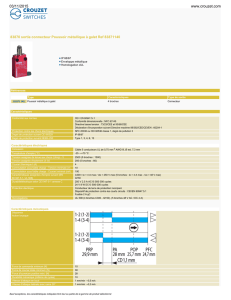

6. Programmation des PLD.

Cahier des charges

Mise en « équation » du problème

Résolution du problème sous forme d’équation logique,

de logigramme ou d’algorithme

Saisie des équations logiques, de la table de vérité, du

logigramme ou de l’algorithme avec le logiciel

Simplification logique

Génération d’un fichier au format JEDEC

Simulation

Programmation du PLD à l’aide du fichier JEDEC et du

programmateur

PLD programmé

Choix du PLD en fonction du nombre d’entrées et de

sorties

Ces étapes sont

effectuées par le

logiciel

1

/

4

100%