circuits numeriques programmables

CIRCUITS NUMERIQUES

PROGRAMMABLES

(PROGRAMMABLE LOGIC DEVICES)

Circuits numériques (re)-configurables par l’utilisateur,

réalisant des fonctions logiques

(combinatoires + séquentielles) de façon matérielle

Contenu de la présentation

1) Introduction des différentes familles

2) SPLD (Simple Programmable Logic Device)

3) EPLD / CPLD (Erasable / Complex Programmable Logic Device)

4) FPGA (Field Programmable Gate Array)

1 - Différentes approches en électronique numérique:

• circuits discrets (TTL, CMOS, ...)

• circuits numériques programmables

•ASICs

contrainte logique

discrète

circuits

numériques

programmables

ASIC

vitesse -++++

densité -++++

coût -+++ (pour très

grosses quantités)

temps de développement +++- -

temps de simulation et de

prototypage -++- -

temps de fabrication -++- -

facilité de mise en œuvre ++- -

modification ultérieure +++- -

risque d’approvisionnement ++ ++ - -

support de l’outil de dévelop-

pement -++++

consommation +-++

Différentes familles de circuits numériques programmables

•PAL (Programmable Array Logic) ou SPLD (Simple Programmable Logic Device)

famille la plus ancienne (introduite par AMD)

technologie:

fusibles (One Time Programmable)

EEPROM (appelation GAL (Generic Array Logic), marque déposée par LATTICE Semiconductor, ou PAL CMOS)

principaux constructeurs: ATMEL, LATTICE Semiconductor, CYPRESS...

•EPLD (Erasable Programmable Logic Device) ou CPLD (Complex Programmable Logic Device)

technologie:

EPROM (effaçable par UV)

EEPROM (effaçable électriquement)

principaux constructeurs: ALTERA, XILINX...

•FPGA (Field Programmable Gate Array)

technologie:

anti-fusibles (non volatile)

SRAM (volatile)

principaux constructeurs: ALTERA, XILINX, ACTEL...

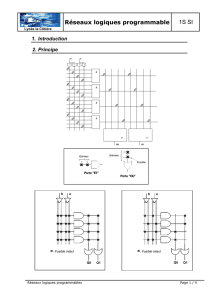

2 - SPLD (Simple Programmable Logic Devices)

circuit numérique programmable le + simple: ROM

entrées: lignes d’adresse

sorties: lignes de données

exemple: 4 mots de 4 bits

Sorties = fonctions logiques des entrées

Décodeur complet pour les entrées (tous les termes produits sont générés)

Mal adapté à la réalisation de fonctions logiques

I1 . I0

I1 . I0

I1 . I0

I1 . I0

I1

I0

O3O2O1O0

exemple:

O0 = (I1 . I0) + (I1 . I0)

décodeur (fixe)

= I1 XOR I0

ET OU

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

1

/

29

100%