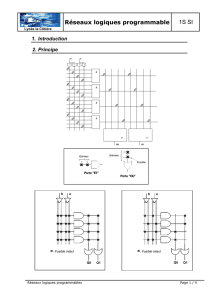

Les circuits logiques programmables - Accueil

Série No 2 GEN1243 Conception de Systèmes Digitaux

19

LOGIQUE PROGRAMMABLE

ET SES OUTILS DE DÉVELOPPEMENT

Motivation

Remplacer les composants discrets par un circuit programmable. Ceci dans le but de

diminuer le coût de production, d'augmenter l'intégration et de protéger le design.

Ø L’origine des différentes sortes de PLD « Programmable Logic Devices » est liée aux

résultats de recherche trouvés dans le milieux des années 1960. À un taux d'un

nouveau produit par mois, les progrès dans ce domaine constituent une partie

importante du rayonnement du parc technologique Silicon Valley.

Historique des circuits logiques programmables

Ø Le premier circuit logique programmable a été mis au point par Harris

Semiconductors et consistait en une matrice de diodes très simple. Ceci ne

représente qu'un élément primitif des premiers PLD.

Ø Les PLD actuels sont plutôt basés sur des réseaux logiques programmables (PLA).

Ce dernier type de PLD a été créé en 1969 par IBM et amélioré par Texas Instruments

(TI), Collins Radio et National Semiconductor.

Ensuite,

Ø Intersil, Signetics et Data I/O ont été parmi les premiers à lancer la vague des PLD

modernes.

Ø Le premier PLD en technologie des transistors MOS a été complété en 1971 par

collaboration avec GE ont commencé une nouvelle série de PLD qu'on appelait réseau

General Electric (GE). Ce circuit effaçable à l'ultraviolet représentait le premier EPLD

(Electrically PLD) disponible sur le marché.

Série No 2 GEN1243 Conception de Systèmes Digitaux

20

Principaux outils de développement avec la logique programmable

Ø Plusieurs compilateurs ont accompagné l'explosion des circuits PLD.

Ø PALASM: constitue la première génération de ces logiciels, ne supportait que les

produits MMI des PAL et nécessitait beaucoup de conversions de données afin

d'obtenir le format de programmation;

Ø ABEL « Advanced Boolean Expression Language » : introduit en 1983 par Data I/O. et

constitue le premier outil universel pour les PLD. C'est un compilateur qui convertit

un code source (fichier) HDL « Hardware Description Language » en un patron de

fusibles « Fusemap ».

Ø Après le lancement des deux compilateurs PALASM et ABEL, une nouvelle

génération permettant de simuler et de vérifier la fonctionnalité totale avant

implantation a été introduite. En effet, MINC a introduit le PLDesigner qui sert à

subdiviser un grand circuit en de petites portions. Suite à ses succès, PLDesigner a

été acheté par Mentor Graphics;

Ø CUPL: introduit en 1981 par Assisted Technology;

Ø AMAZE (Automated Map & Zap of Equations): introduit par Signetics;

Ø PLAN (Programmable Logic Analysis): introduit par National Semiconductor

Ø APEEL (Assembler PEEL): introduit par ICT;

Ø VHDL « VHSIC Hardware Description Language »: introduit en 1987 par le

département de la Défense américaine en collaboration avec le IEEE. Comme ABEL,

c'est un compilateur qui convertit un code source (fichier) HDL en un patron de

fusibles.

Ø On note de nouveaux produits importants tels que: Tango-PLD (Accel Technologies),

Log/iC (ISDATA) Schema-PLD (Omation) OrCAD/PLD (ORCAD Systems), SP11 (Pistohl

Electronic Tool), Synopsys, Texas Instruments, etc..

Série No 2 GEN1243 Conception de Systèmes Digitaux 2

1

ASIC

Application Specific Integrated Circuits

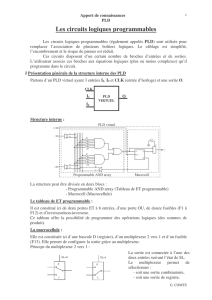

Ø Circuits intégrés destinés à des applications spécifiques. La technologie des circuits

ASIC « Application Specific Integrated Circuits » a été introduite afin de remplacer les

composants discrets par un nombre minimum de circuits intégrés.

Ø Cela contribue à diminuer le coût de production, à augmenter l'intégration et à

protéger le design.

Ø La conception et la réalisation d'un circuit ASIC peuvent être complétées par l'une ou

l'autre des méthodes suivantes :

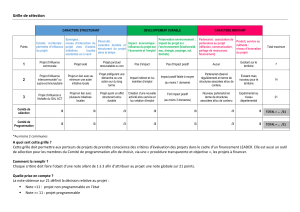

Techniques de réalisation de circuits intégrés destinés à des applications spécifiques (ASIC)

(Semi-custom) Cellules

standards: nécessite une phase

complète de fabrication

Matrice de

portes

remplace 500

SSI et MSI

"Gate Array"

PGA (100K)

masques.

Normalisées avec masques dédiés. UAL,

mémoires, processeurs etc.

(Full custom)

Circuit dédié

Processeurs SoC, PCI (PC Interface

controllers), etc.. Necessite un nombre

varié de transistors et une phase

complète de fabrication.

-Analog

-Digital

-Bio..

Architecture micro-programmable

Bit-Slice necessite un séquenceur

d'interruption et une UAL.

Configuration des interconnections par

une RAM, ROM ou un

microprocesseur.

Série No 2 GEN1243 Conception de Systèmes Digitaux

22

Les circuits logiques programmables (PLD)

Ø Les PLD ont connu des succès remarquables.

Ø Ces succès sont dus à la préconception des fonctions élémentaires (ET, OU, Bascule,

etc.),

Ø Facilite la conception, réduit le temps de mise en marché et implique un faible coût de

fabrication.

Ø Inconvénients : limitation du nombre de portes par circuit.

Ø La conception des circuits par PLD est basée sur la synthèse des fonctions sous la

forme de somme des produits SdP (SoP).

Ressources matérielles de circuits logiques programmables

Ø Un circuit logique programmable contient généralement trois types de ressources ou

de fonctions de base:

1. Fonction combinatoire ou séquentielle: la reconfiguration de cette fonction peut

être basée sur une table de vérité (LUT), un jeu de multiplexeurs, un plan ET-OU,

différentes portes logiques, ou un ensemble de transistors.

2. Bloc d'entrée/sortie: ce type de fonction réalise un circuit logique d'entrée/sortie

bidirectionnel. Il est basé sur des bascules, des bistables, contrôle du « slew-rate

», « pullup » et « pulldown ».

3. Interconnexions : Circuiterie servant à accommoder les deux types

d'interconnexions: locale et globale. L'importance de ce type de fonction tient au

fait qu'il faut assurer une flexibilité maximale.

N.B : Il faut noter qu'une technique de distribution d'horloge est utilisée pour éviter le

«skew » d'horloge lors de l'opération.

Série No 2 GEN1243 Conception de Systèmes Digitaux

23

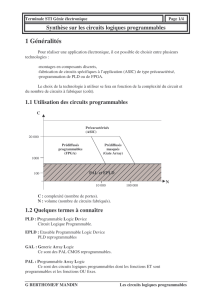

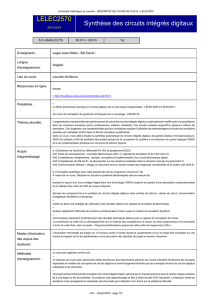

Catégories de PLD

Les catégories sont:

Ø PLE: Programmable Logic Element (PROM)

- Plan ET fixe

- Plan OU programmable

Schéma simplifié des différents circuits PLD (PROM, PAL et PLA)

Ø PAL: Programmable Array Logic

- ET programmable

- OU fixe

Ø PLA:

Programmable

Logic Array

- ET

programmable

- OU

programmable

6

6

7

7

8

8

9

9

10

10

1

/

10

100%