Module:

Structure machine 2

Université Djilali Liabés- Sidi Bel Abbes

Mohammed Fethi KHALFI

Fethi.Khalfi@yahoo.fr

Chapitre 2 : La logique combinatoire

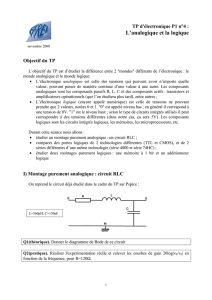

Introduction

La donnée de base manipulée par la machine est le bit

qui ne peut prendre quedeux valeurs: 0et 1.

Les transistors constituent les circuits physiques de la

machine.1,4 milliards de transistors pour le Core i7

Ces circuits physiques sont construits à partir de

circuits logiques, c'est-à-dire de circuits

des

intégrés

opération

spécialisés, destinés à réaliser

arithmétiques et logiques.

Tout ordinateur est donc conçu

une

àpartir de circuits

intégrés qui ont tous fonction spécialisée

(décodage, multiplexage,encodage,comparaison,

opérations arithmétiques (addition,soustraction,...)) 2

Les circuits combinatoires

Objectifs

Apprendre la structure de quelques circuits

combinatoires souvent utilisés (demi additionneur ,

additionneur complet,……..).

Apprendre

combinatoires

complexes.

comment utiliser des circuits

pour concevoir d’autres circuits plus

3

1.Les Circuits combinatoires

Un circuit combinatoire est un circuit numérique

dont les sorties dépendent

Si=F(Ei)

Si=F(E1,E2,….,En)

uniquement des entrées.

S1

S2

..

Sm

E1

E2

..

En

Schéma Bloc

possible d’utiliser des circuits combinatoires

• C’est

pour réaliser d’autres circuits plus complexes.

4

Circuit

combinatoire

Exemple de Circuits combinatoires

Voici une liste des principales fonctions

combinatoires :

standards

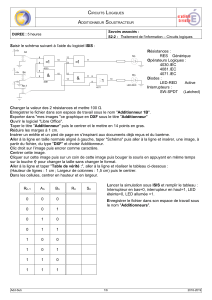

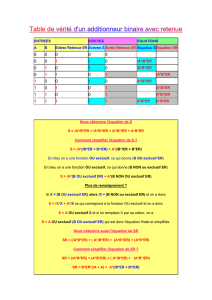

DemiAdditionneur

Additionneur complet

Comparateur

Multiplexeur

Démultiplexeur

Encodeur

Décodeur

1.

2.

3.

4.

5.

6.

7.

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

1

/

27

100%