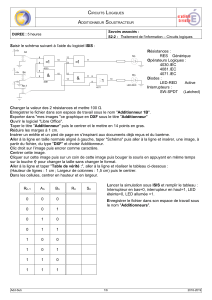

additionneur

Table de vérité d'un additionneur binaire avec retenue

ENTREES

SORTIES

EQUATIONS

A

B

Entree Retenue ER

Somme S

Sortie Retenue SR

Equation S

Equation SR

0

0

0

0

0

0

0

1

1

0

/A*/B*ER

0

1

0

1

0

/A*B*/ER

0

1

1

0

1

/A*B*ER

1

0

0

1

0

A*/B*/ER

1

0

1

0

1

A*/B*ER

1

1

0

0

1

A*B*/ER

1

1

1

1

1

A*B*ER

A*B*ER

Nous obtenons l'équation de S

S = /A*/B*ER + /A*B*/ER + A*/B*/ER + A*B*ER

Comment simplifier l'équation de S ?

S = /A*(/B*ER + B*/ER) + A*(/B*/ER + B*ER)

En bleu on a une fonction OU exclusif, ce qui donne (B OU exclusif ER)

En bleu on a une fonction OU exclusif, ce qui donne (B NON ou exclusif ER)

S = /A*(B OU exclusif ER) + A*(B NON OU exclusif ER)

Plus de renseignement ?

Si X = (B OU exclusif ER) alors /X = (B NON ou exclusif ER) et on a donc

S = /A*X + A*/X ce qui correspond à la fonction OU exclusif et on a donc

S = A OU exclusif X et si on remplace X par sa valeur, on a

S = A OU exclusif (B OU exclusif ER) qui est donc l'équation finale et simplifiée.

Nous obtenons aussi l'équation de SR

SR = (/A*B*ER) + ( A*/B*ER) + (A*B*/ER) + (A*B*ER)

Comment simplifier l'équation de SR ?

SR = (/A*B*ER) + (A*B*ER) + ( A*/B*ER) + (A*B*/ER)

SR = B*ER*(/A + A) + A*(/B*ER + B*/ER)

En bleu on a une fonction OU exclusif, ce qui donne (B OU exclusif ER)

SR = B*ER*(/A + A) + A*(B OU exclusif ER)

En noir on a (/A + A), ce qui donne 1

SR = (B * ER) + A*(B OU exclusif ER)

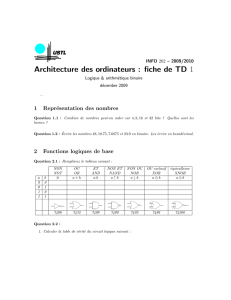

Demi additionneur binaire

Considérons la table

X

Y

S

R

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

qui nous donne le résultat de la somme de deux digits binaires S ainsi que la retenue R (carry en

anglais), et dont on tire les relations suivantes:

S = X.Y + X.Y qui représente la fonction OU exclusif (S=1 si X ou Y mais pas les deux sont à 1)

R = X.Y

Le circuit réalisant ces fonctions porte le nom de demi-additionneur. Il peut être réalisé selon le

schéma ci-dessous.

soit exclusivement avec des circuits NOR

additionneur complet

Pour faire un additionneur complet il faut un circuit qui additionne 2 digits et la retenue de la somme

des digits de poids immédiatement inférieur et répondant à la table

X

Y

R-1

S

R

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

Cette table correspond aux deux relations

S = R-1 (X.Y + X.Y) + R-1 (X.Y + X.Y)

R = X.Y + R-1 (X.Y + X.Y)

Si l'on pose S' = X.Y +X.Y on voit que S = R-1 S' + R-1 S'

Cette fonction S' est obtenue à l'aide d'un demi-additionneur d'entrée X et Y tandis que S est obtenue

avec un demi-additionneur d'entrée S' et R-1. Enfin R est la somme booléenne des sorties R1 et R2

de ces deux demi-additionneurs

additionneur parallèle

Ce cas est typiquement exploité dans le microprocesseur. Soit 2 nombres de 4 digits X1, X2, X3, X4

et Y1, Y2, Y3, Y4 que l'on désire additionner. Ces nombres sont stockés dans deux registres dont les

sorties sont commandées en parallèle. Le dispositif est du type ci-dessous :

Le signal d'horloge appliqué sur la ligne de départ permet la transmission des infos Xn et Yn

simultanément aux 4 additionneurs. Après un décalage dans le temps suffisamment long pour que les

retenues générées puissent intervenir dans l'addition le résultat est lu en Z1, Z2, Z3, Z4 et R après le

signal d'horloge sur la ligne résultat. Ce résultat est enregistré dans un nouveau registre.

able de vérité de la fonction xor et circuits équivalents

Le circuit suivant réalise l'addition ( au sens arithmétique ) de 2 nombres binaires de 1 bit.

A

B

Somme

0

0

0

0

1

1

1

0

1

0

1

0

A

B

Report

0

0

0

0

1

0

1

0

0

0

1

1

A

B

Rin

S

Rout

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

1

/

13

100%