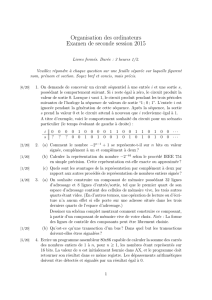

Première session 2009

Informatique — Ordinateurs et syst`emes d’exploitation

Examen ´ecrit du jeudi 4 juin 2009

Livres ferm´es. Dur´ee : 3 heures 1/2.

Veuillez r´epondre `a chaque question sur une feuille s´epar´ee sur laquelle figurent nom,

pr´enom et section. Soyez bref et concis, mais pr´ecis.

Les ´etudiants inscrits en 1re ann´ee de bachelier en sciences de l’ing´enieur, orientation

ing´enieur civil ne doivent pas r´epondre `a la question 5.

1. On demande de construire un circuit s´equentiel capable de contrˆoler la sonnerie et

la lampe de demande d’arrˆet d’un autobus. Le circuit poss`ede deux entr´ees :

–ivaut 1 lorsqu’au moins un des boutons poussoirs de demande d’arrˆet situ´es dans

l’autobus est enfonc´e, et 0 sinon.

–pvaut 1 lorsque les portes de l’autobus sont ouvertes, et 0 sinon.

Le circuit poss`ede deux sorties : une sonnerie set une lampe `. Leur comportement

est le suivant : lorsqu’une demande d’arrˆet est re¸cue (par l’entr´ee i) lorsque les

portes sont ferm´ees, la lampe `passe `a 1, et le reste jusqu’`a ce que les portes de

l’autobus soient ouvertes par le conducteur. En outre, la sonnerie retentit pendant

une p´eriode d’horloge. Si des demandes d’arrˆet ult´erieures arrivent avant que les

portes de l’autobus ne soient ouvertes, la sonnerie ne doit plus retentir. Lorsque les

portes de l’autobus s’ouvrent, la lampe doit s’´eteindre jusqu’`a la prochaine demande

d’arrˆet, moment auquel le processus recommence.

2. (a) Quel est le plus grand nombre naturel repr´esentable de fa¸con exacte dans le

standard IEEE 754 double pr´ecision ? Justifiez votre r´eponse. Quelle est sa

repr´esentation ?

(b) Parmi les proc´ed´es de repr´esentations “par valeur sign´ee”, “par compl´ement `a

un”, “par compl´ement `a deux” et “IEEE 754”, lequel est utilis´e en pratique dans

les processeurs modernes pour repr´esenter et manipuler des nombres entiers

sign´es ? Pour quelles raisons ?

(c) Donnez la plus petite repr´esentation du nombre −109 dans chacun des formats

suivants :

i. compl´ement `a un ;

ii. compl´ement `a deux ;

iii. IEEE 754 simple pr´ecision.

3. (a) Donnez la forme g´en´erale d’une m´emoire vive de type m×n, en d´etaillant le

nombre et le rˆole de chacune de ses entr´ees et sorties.

(b) De quelle mani`ere peut-on combiner des composants de m´emoire vive afin d’ob-

tenir un composant poss´edant un plus grand nombre de cellules, la taille des

cellules restant identique ? D´etaillez.

1

4. On demande d’´ecrire un programme assembleur 80x86 d´eterminant la valeur maxi-

male des observations issues d’un ensemble d’exp´eriences.

Ces donn´ees sont organis´ees en m´emoire de la mani`ere suivante. Le nombre d’exp´e-

riences est contenu dans le registre CX ; le nombre d’observations par exp´erience est

contenu dans le registre DX. Ces deux valeurs peuvent ˆetre suppos´ees non nulles.

Chaque exp´erience consiste en un tableau d’observations, chacune de ces obervations

´etant repr´esent´ee par une valeur enti`ere non sign´ee cod´ee sur 8 bits. Les adresses (sur

16 bits) des CX tableaux d’exp´eriences sont contenues dans un tableau point´e par le

registre BX.

A la fin de l’ex´ecution du programme, le registre AL doit contenir la valeur maximale

des observations, toutes exp´eriences confondues.

En guise d’illustration, le sch´ema ci-dessous repr´esente une situation o`u il y a 3

exp´eriences, chacune contenant 2 observations. Le registre AL doit contenir la valeur

8 `a la fin de l’ex´ecution du programme.

6 4 2 8 4 1

BX

DX = 2 DX = 2 DX = 2CX = 3

5. Les ´etudiants inscrits en 1re ann´ee de bachelier en sciences de l’ing´enieur, orientation ing´e-

nieur civil ne doivent pas r´epondre `a cette question.

(a) Dans quels ´etats un processus peut-il se trouver ? D´ecrivez bri`evement chacun

d’entre-eux. Quelles sont les transitions possibles entre ces ´etats ?

(b) Quelles sont les raisons pour lesquelles la gestion de la m´emoire est habituelle-

ment confi´ee aux syst`emes d’exploitation ?

2

Annexe 1 : Modes d’adressage des instructions 80x86

MOV

Op.1 Op.2 Op.1 Op.2

rαrαrαpα

mαrαrαiα

rαmαpαiα

pαrαmαiα

XCHG

Op.1 Op.2

rαrα

mαrα

pαrα

rαmα

rαpα

PUSH

Op.1

r16

m16

i16

POP

Op.1

r16

m16

ADD, SUB, AND, OR, XOR, CMP

Op.1 Op.2 Op.1 Op.2

rαrαrαpα

mαrαrαiα

rαmαpαiα

pαrαmαiα

r16 i8 p16 i8

m16 i8

INC, DEC, MUL, NOT

Op.1

rα

mα

pα

JMP, LOOP, CALL

Op.1

i16

r16

m16

p16

r= registre, i= imm´ediat, m= direct, p= indirect ou indirect index´e, α= 8 ou 16.

Annexe 2 : Instructions de saut conditionnel

Instr. Condition de saut

JE Op1 =Op2

JNE Op1 6=Op2

JG Op1 >Op2 (valeurs sign´ees)

JGE Op1 ≥Op2 (valeurs sign´ees)

JL Op1 <Op2 (valeurs sign´ees)

JLE Op1 ≤Op2 (valeurs sign´ees)

JA Op1 >Op2 (valeurs non sign´ees)

JAE Op1 ≥Op2 (valeurs non sign´ees)

JB Op1 <Op2 (valeurs non sign´ees)

JBE Op1 ≤Op2 (valeurs non sign´ees)

3

1

/

3

100%