projet vhdl

IUT GEII de Neuville sur Oise – TP FPGA – 2015

Pr. Olivier ROMAIN

1

PROJET VHDL

Jeux du Simon

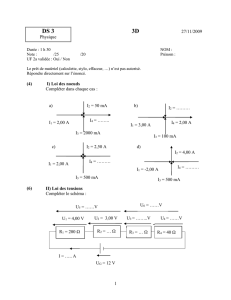

Simon est un jeu de société des années 70-80 de forme circulaire divisé en quatre quarts de couleur différentes,

rouge, vert, bleu et jaune. A chaque couleur est associé un son caractéristique. Le principe du jeu consiste à

répéter une séquence aléatoire des quatre couleurs qui s’affiche. Le jeu affiche une couleur et le joueur répète

cette couleur. Si la couleur est fausse, le joueur a perdu et le jeu recommence depuis le début. Si la couleur est

bonne, le jeu ajoute une nouvelle couleur à la suite de la précédente et le joueur doit reproduire l’intégralité de la

séquence. Plus le joueur reproduit fidèlement la séquence et plus l’affichage de la séquence est rapide et longue.

L’objectif du jeu est de réaliser la plus longue séquence produite. Les joueurs jouent à tour de rôle.

Une illustration du jeu est donnée ci-dessous et une vidéo est disponible à l’adresse suivante

http://olivieromain.free.fr/simon.avi

Figure 1 : Jeu du simon

L’objectif de ce projet est de réaliser ce jeu à partir d’une carte FPGA. L’affichage des séquences lumineuses

sera réalisé à partir d’un écran. Le son sera reproduit à partir du codec audio disponible sur la carte (partie

optionnelle).

Le projet comporte trois parties :

• Génération des séquences aléatoires

• Contrôleur VGA pour l’affichage des couleurs

• Machine à états pour le contrôle du jeu

IUT GEII de Neuville sur Oise – TP FPGA – 2015

Pr. Olivier ROMAIN

2

Partie I. Générateur Pseudo Aléatoire : Automate Cellulaire

Il existe différentes méthodes pour générer des séquences pseudo-aléatoire de nombre. La plus connue est la

méthode basée sur une boucle fermée d’un registre à décalage sur lui même suivant un polynôme générateur. Ici,

nous allons utiliser une seconde technique basée sur les automates cellulaires. Avant de coder en VHDL cet

automate, une brève introduction est donnée ci-dessous.

Le nom d’automate cellulaire peut sonner comme une oxymore. D’un côté le mot ‘automate’ suggère l’artificiel,

la mécanique, le logique, le déterminisme et de l’autre côté le mot ‘cellulaire’ renvoie au naturel, à la biologie et

au vivant et donc à l’imprévisible. Comment deux concepts aussi opposés peuvent-ils s’associer au sein d’un

même nom pour désigner un objet ?

Dans les années quarante, le mathématicien Stanislas Ulam donna naissance aux

automates cellulaires en modélisant la croissance des cristaux sur une grille. Son

point de départ était un quadrillage, soit un espace à deux dimensions définissant

un nombre fini de cases ou de cellules. Chacune des cellules était booléenne :

allumé ou éteint. A l’état de départ, t0, certaines cellules de façon arbitraire étaient

allumées. A partir de cette configuration initiale, les états des cellules évoluaient

en fonction de règles de voisinage entre cellules. Par exemple, si une cellule

donnée était en contact avec deux cellules allumées, alors elle s'allumait, sinon elle

s'éteignait. Ces mécanismes simples permettaient de générer des figures

complexes qui, dans certains cas, pouvaient se répliquer.

Dans les mêmes années, John Von Neumann, un collègue de Ulam, travaillait sur les mécanismes

mathématiques de machines auto-réplicatives, c'est-à-dire des machines capables de produire une copie d’elle-

même.

"... living organisms are very complicated aggregations of elementary parts, and by any reasonable theory of

probability or thermodynamics highly improbable. That they should occur in the world at all is a miracle of the

first magnitude; the only thing which removes, or mitigates, this miracle is that they reproduce themselves.

Therefore, if by any peculiar accident there should ever be one of them, from there on the rules of probability do

not apply, and there will be many of them, at least if the milieu is reasonable."

John Von Neumann, Theory of Self-Reproducing Automata.

source : The artificial Self-replication page by Moshe Sipper.

A partir des travaux de Ulam, John von Neumann construisit une première implémentation de l’auto

reproduction. Ulam avait conçu des programmes intégrant des règles simples qui permettait la génération de

motif auto-reproductif et John Von Neumann inventa alors le Kinématon. Le ‘Kinématon est un automate

cellulaire bidimensionnel intégrant environ 200.000 cellules à 29 états, avec un voisinage de 5 cellules (1 cellule

cible + 4 voisines). L’objectif de Von Neumann au travers le Kinématon était de réaliser un constructeur

universel, capable de répliquer à l’identique toute structure dont on lui a donné le plan.

Un automate cellulaire se caractérise par 4 paramètres :

• Sa dimension : un automate cellulaire est le plus généralement 1D (ligne), 2D (matrice), ou de

dimension N. Toutes les cellules qui constituent l’automate sont mises à jours de manière synchrone.

• Le voisinage d’une cellule : celui-ci détermine le nombre de cellules qui participeront à la détermination

de l’état futur de la cellule en cours d’étude. Dans le cas d’une ligne, une cellule possède un voisinage

de deux. Ces deux cellules détermineront l’état de cellule centrale à l’instant t+1. Toutes les cellules

utilisent les mêmes règles pour déterminer leur état suivant.

• Son Alphabet ou espace d’état : Cet alphabet correspond à l’ensemble de tous

les états qu’une cellule peut prendre. Le plus souvent ils sont Booléen (2 états) mais il

existe des exemples d’automates cellulaires ou l’alphabet est supérieur à 2, comme dans

le cas du Kinématon.

• Sa fonction de transition : elle correspond aux règles de passage d’un état présent à un état futur d’une

cellule en fonction de son voisinage. Le nombre de fonction de transition correspond au nombre de

voisinage à la puissance nombre de configuration de voisinage.

IUT GEII de Neuville sur Oise – TP FPGA – 2015

Pr. Olivier ROMAIN

3

Il existe de nombreuse réalisation d’automates cellulaires dont les plus connus sont :

• L’automate élémentaire de Wolfram

• La boucle auto réplicante de Langton

• Le jeu de la vie de Conway

Les automates cellulaires trouvent de nombreuses applications dans des domaines très divers, de la conception

d’ordinateurs massivement parallèles à la simulation de la propagation des deux de forêts en passant par la

conception de générateur de séquences pseudo aléatoires utiles en télécommunication.

Automate cellulaire simple générateur de séquencse pseudo-aléatoires

Un automate cellulaire simple ou automate de Wolfram consiste en une grille unidimensionnelle de cellules ne

pouvant prendre que deux états (0 ou 1), avec un voisinage constitué, pour chaque cellule, d'elle-même et des

deux cellules qui lui sont adjacentes, une cellule voisine de gauche et une cellule voisine de droite.

Chacune des cellules pouvant prendre deux états, il existe 23=8 configurations possibles d'un tel voisinage.

Pour que l'automate cellulaire fonctionne, il faut définir quel doit être l'état, à la génération suivante, d'une

cellule pour chacun de ces motifs. Il y a 28 = 256 façons différentes de s'y prendre, soit donc 256 automates

cellulaires différents pouvant être simulés sur une telle grille.

Ces automates sont bouclés, c'est à dire que si l'automate a une taille n, la cellule 0 à comme voisin de gauche la

cellule n − 1, et la cellule n − 1 a comme voisin de droite la cellule 0. Considérons l'automate cellulaire défini

par la table suivante qui donne la valeur de la cellule centrale à l'instant t + 1 en fonction de la valeur de la

cellule et de ses cellules adjacentes à l'instant t :

Valeur de la cellule i-1 à l’instant t

1

1

1

1

0

0

0

0

Valeur de la cellule i à l’instant t

1

1

0

0

1

1

0

0

Valeur de la cellule i+1 à l’instant t

1

0

1

0

1

0

1

0

Valeur de la cellule i à l’instant t+1

0

0

0

1

1

1

1

0

Cela signifie que si par exemple, à un temps t donné, une cellule est à l'état 1 , sa voisine de gauche à l'état 1 et

sa voisine de droite à l'état 0, au temps t + 1 elle sera à l'état 0.

L’équation de la fonction de transition régit complètement le séquencement de l’automate cellulaire. Il existe des

équations qui permettent de d’obtenir un comportement pseudo-aléatoire comme par exemple en

prenant l’équation ci-dessous et en initialisant l’automate à 1.

€

c(i)t+1=(c(i−1)t+c(i)t)⊕c(i+1)t

Voisinage

Cellule 0

Cellule 1

Cellule 2

Cellule N

1

0

0

1

Fonction de

transition

Fonction de

transition

Fonction de

transition

Fonction de

transition

IUT GEII de Neuville sur Oise – TP FPGA – 2015

Pr. Olivier ROMAIN

4

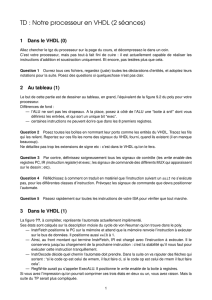

En prenant l’une des sorties de l’automate c(i) on récupère alors une séquence pseudo aléatoire comparable aux

générateur obtenus à l’aide de bascules D et dont certaines sont une porte Xor suivant un polynôme

caractéristique comme ci-dessous :

Figure 2 : Exemple de générateur pseudo-aléatoire à 3 bascules D

Remarque

Des informations supplémentaires sont disponibles : https://fr.wikipedia.org/wiki/Automate_cellulaire

Travail à réaliser

1. Créer un projet sous Quartus et nommer le simon

2. Créer un fichier bdf simon.bdf

3. Créer un fichier VHDL automate.

4. Ecrire le code VHDL d’un automate cellulaire générique sur 8 cellules.

a. L’entité de l’automate prendra une horloge dont la fréquence

b. Un signal de reset

c. Un signal de start

d. Un signal de sortie correspondant à la séquence aléatoire

5. Simuler le fonctionnement.

6. Déterminer la longueur de la séquence en fonction de l’état initial.

La principale limitation de ce générateur est la périodicité de la longueur de la séquence. Elle a pour

conséquence de rendre déterministe le générateur. Pour palier à ce problème, on va pré-positionner les entrées

des bascules D avant le démarrage de la séquence.

7. Modifier l’entité pour prendre en entrée un bus de 8 bits. Chaque bit du bus pré-positionnera l’entrée de

la bascule correspondante. Par exemple, le 3ème bit pré-positionnera l’entrée de la 3ème bascule. Si le 3ème

bit est à ‘1’, la 3ème bascule D prendra un 1 en entrée avant le démarrage du générateur (signal de start).

Le pré-positionnement sera réalisé au moyen des 8 switchs SW0 … SW7.

8. Simuler le fonctionnement et déterminer la longueur L de la séquence en fonction de la valeur V des

switchs.

9. Programmer la carte et observer la séquence générée. La sortie sera affectée à la broche 2 de J4

(PIN_AB16) (cf. reference manual DE1)

10. Tracez la courbe L en fonction de V.

11. Déterminer la valeur de V permettant d’obtenir la plus grande longueur.

12. Conclusion

Pour augmenter la longueur de la séquence, une autre solution consiste à modifier le rebouclage. Sur la figure 2,

il existe deux possibilités ; injecter sur la première bascule le résultat de Q2 xor Q1 ou d’injecter Q2 xor Q0.

13. Modifier le design de votre automate afin de tester les 7 configurations suivantes :

a. Injecter sur D0 le résultat de Q7 xor Q6

IUT GEII de Neuville sur Oise – TP FPGA – 2015

Pr. Olivier ROMAIN

5

b. Injecter sur D0 le résultat de Q7 xor Q5

c. Injecter sur D0 le résultat de Q7 xor Q4

d. Injecter sur D0 le résultat de Q7 xor Q3

e. Injecter sur D0 le résultat de Q7 xor Q2

f. Injecter sur D0 le résultat de Q7 xor Q1

g. Injecter sur D0 le résultat de Q7 xor Q0

14. Pour chaque configuration déterminer la longueur maximale L en fonction de la valeur V. Reporter

dans le graphe de la question 7

15. Remplir le tableau ci-dessous et le reporter dans votre rapport.

Configuration

Valeur V en décimal donnant Lmax

Longueur Maxi - Lmax

a

b

c

d

e

f

g

16. Consigner tous les développements et résultats dans votre rapport.

17. Réaliser un bloc graphique que vous intégrer dans votre fichier structurel simon.bdf.

18. Fin contrôler l’ensemble des résultats par l’enseignant avant de passer à l’étape 2 du projet.

6

6

7

7

8

8

9

9

10

10

11

11

1

/

11

100%

![Exercice 1 [Bac Liban 2016] : Solution page 1 Un automate peut se](http://s1.studylibfr.com/store/data/001876471_1-aac3bd8ca65b5f5251c8e166c1447a0c-300x300.png)