TD : Notre processeur en VHDL (2 séances)

TD : Notre processeur en VHDL (2 séances)

1 Dans le VHDL (0)

Allez chercher le tgz du processeur sur la page du cours, et décompressez-le dans un coin.

C’est votre processeur, mais pas tout-à fait fini de cuire : il est actuellement capable de réaliser les

instructions d’addition et soustraction uniquement. Et encore, pas testées plus que cela.

Question 1

Ouvrez tous ces fichiers, regardez (juste) toutes les déclarations d’entités, et adoptez leurs

notations pour la suite. Posez des questions si quelquechose n’est pas clair.

2 Au tableau (1)

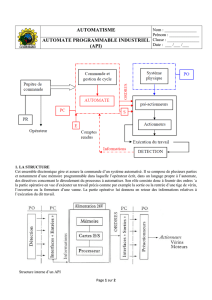

Le but de cette partie est de dessiner au tableau, en grand, l’équivalent de la figure 9.2 du poly pour votre

processeur.

Différences de fond :

—

l’ALU ne sort pas les drapeaux. A la place, posez à côté de l’ALU une “boite à snif” dont vous

définirez les entrées, et qui sort un unique bit “exec”.

— certaines instructions ne peuvent écrire que dans les 8 premiers registres.

Question 2

Posez toutes les boîtes en nommant leur ports comme les entités du VHDL. Tracez les fils

qui les relient. Reportez sur ces fils les noms des signaux du VHDL fourni, quand ils existent (il en manque

beaucoup).

Ne détaillez pas trop les extensions de signe etc : c’est dans le VHDL qu’on le fera.

Question 3

Par contre, définissez soigneusement tous les signaux de contrôle (les write enable des

registres PC, IR (instruction register) et exec ; les signaux de commande des différents MUX qui apparaissent

sur le dessin ; etc).

Question 4

Réfléchissez à comment on traduit en matériel que l’instruction suivant un

snif

ne s’exécute

pas, pour les différentes classes d’instruction. Prévoyez les signaux de commande que devra positionner

l’automate.

Question 5 Passez rapidement sur toutes les instructions de votre ISA pour vérifier que tout marche.

3 Dans le VHDL (1)

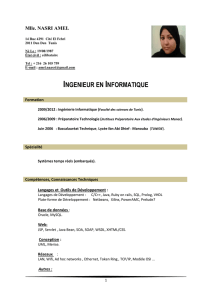

La figure ??, à compléter, représente l’automate actuellement implémenté.

Ses états sont calqués sur la description moisie du cycle de von Neuman qu’on trouve dans le poly.

—

InstrFetch positionne le PC sur la mémoire et attend que la mémoire renvoie l’instruction à exécuter

sur le bus de données. Il positionne aussi weIR à 1.

—

Ainsi, au front montant qui termine InstrFetch, IR est chargé avec l’instruction à exécuter. Il le

conservera jusqu’au chargement de la prochaine instruction : c’est la stabilité qu’il nous faut pour

exécuter cette instruction tranquillement.

—

InstrDecode décide quel chemin l’automate doit prendre. Dans la suite on va rajouter des flèches qui

sortent : “si le code op est celui de wmem, il faut faire ci, si le code op est celui de rmem il faut faire

cela”.

— RegWrite aurait pu s’appeler ExecALU. Il positionne le write enable de la boite à registres.

Si vous avez l’impression qu’on pourrait comprimer ces trois états en deux ou un, vous avez raison. Mais la

suite du TP serait plus compliquée.

1

Question 6

Ouvrez

control_FSM.vhdl

et comprenez comment il est organisé. Placez dans chaque état

les signaux de contrôle levés par cet état.

Question 7

Dans quel état réalise-t-on l’incrément de PC ? Est-ce que cela va nous permettre d’implé-

menter le snif ?

Question 8

Tous les registres sont initialisés à 0 (voir

reg_file.vhd

). Sachant cela, ressortez votre

assembleur, écrivez un programme qui réalise l’addition de 5 et 7 en n’utilisant que des

add

, placez son

code au début de la mémoire, et regardez-le s’exécuter dans gtkwave. Pour voir se dérouler le cycle,

observez bien la valeur du registre d’état de l’automate : ce sera utile pour débugger la suite.

Question 9

Implémentez

snif

sans toucher à l’automate. Il faut un peu hacker le VHDL tout de même.

Pour le débuggage, on rappelle que vous pouvez laisser gtkwave ouvert (réglé pour montrer l’état, le PC, et

quelques autres signaux qui vous intéressent) et vous contenter de “reload waveform” entre deux make.

4 Retour au tableau

Question 10

Ajoutez à l’automate et au dessin du proc ce qu’il faut pour

rmem

et

wmem

. Implémentez et

testez au fur et à mesure sur des petits programmes bien choisis.

Question 11

Ajoutez à l’automate et au dessin du proc ce qu’il faut pour

jump

,

call

et

return

. Implé-

mentez et testez au fur et à mesure sur des petits programmes bien choisis.

FIGURE 1 – Ici, bientôt, construction d’un cycle de von Neumann

InstrFetch

XXXXXXXXX

start

InstrDecode

XXXXXXXXX

RegWrite

XXXXXXXXX

IllegalInstr

XXXXXXXXX

codeOp ∈ALU

codeOp /∈ALU

2

1

/

2

100%

![Exercice 1 [Bac Liban 2016] : Solution page 1 Un automate peut se](http://s1.studylibfr.com/store/data/001876471_1-aac3bd8ca65b5f5251c8e166c1447a0c-300x300.png)