TP SPICE

Département Micro-électronique et

télécommunications

Deuxième année – 2003/2004

TP Spice

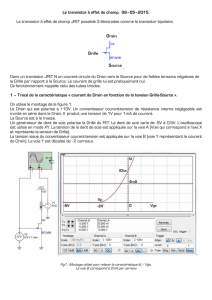

CGD

RS

D

rDS

S’

B

gmVGS

gmBSVBS

CGS

CGB

CBS

CBD

RD

D’

S

B

GCGD

RS

D

rDS

S’

B

gmVGS

gmBSVBS

CGS

CGB

CBS

CBD

RD

D’

S

B

G

Pascal MASSON

Ecole Polytechnique Universitaire de Marseille

Laboratoire Matériaux et Micro-électronique de Provence (L2MP)

2

3

Table des matières

La programmation.............................................................................................. 5

Description du transistor MOS ......................................................................... 9

Prise en main du logiciel ................................................................................. 15

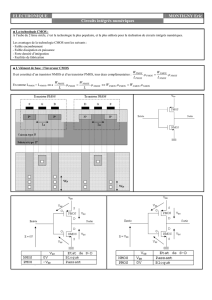

Simulation d’un inverseur CMOS ................................................................... 17

4

5

La programmation

I. Les différents niveaux de programmation

Il existe quatre méthodes pour décrire un circuit électronique avec un simulateur :

1) Avec le dessin des différents niveaux de masques destinés à la fabrication des

composants (TMOS, diodes, résistance…)

2) Avec la netlist qui décrit les composants et les connexions entre eux.

3) Avec le dessin du schéma électrique (placement des composants et connexions entre

eux avec des fils).

4) Avec la description d’une fonction. Le logiciel génère seul le schéma électrique avec

comme paramètres d’optimisation la surface de silicium utilisée, le temps de

propagation…

On remarquera que la méthode 1) est très proche du composant puisqu’il décrit sa forme ainsi

que la forme des connexions entre les composants.

Les méthodes 2) et 3) sont très proches avec une plus grande rapidité d’exécution du circuit

pour le point 4).

La méthode 4) ne nécessite pas de notions très poussées en électronique ou en physique mais

de solides compétences en programmation.

Donc en allant de la méthode 1) à la méthode 4) on accélère le temps de réalisation d’un

circuit et en allant de la méthode 4) à la méthode 3) on s’approche de la description des

composants élémentaires. Lors de la conception d’un circuit intégré, les quatre méthodes de

description peuvent être utilisées. Dans le cadre de l’initiation au logiciel SPICE, nous allons

utiliser les méthodes 2) et 3).

II. La programmation par netlist

Dans ce paragraphe, nous décrivons la génération d’un circuit électrique à partir de la netlist.

Il est bon de signaler qu’en fonction de la version du logiciel utilisée (plus ou moins récente) les

instructions décrites ici peuvent être légèrement différentes. Il est donc préférable d’assimiler ici

la philosophie générale de la création d’une netlist.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

1

/

19

100%