Fichier pdf

Slide 1

Architectures parall`

eles: Un aperc¸u

1. Pourquoi des machines parall`

eles?

2. Classification de Flynn

3. Processeurs modernes et parall´

elisme

4. ´

Evolution des architectures parall`

eles

5. Rˆ

ole et gestion des caches

6. Mod`

eles de

consistence

de m´

emoire

Slide 2

1 Pourquoi des machines parall`

eles?

•Am´

eliorations importantes au niveau des micro-processeurs

–Augmentation de la vitesse d’horloge ≈30 % par ann´

ee

–Augmentation de la densit´

e des circuits ≈40 % par ann´

ee

•mais...

•Plusieurs applications ne peuvent pas ˆ

etre trait´

ees en un temps raisonnable sur un ordina-

teur traditionnel

–simulation et analyse de ph´

enom`

enes physiques ou biologiques, e.g., pr´

ediction m´

et´

eo-

rologique, physique atomique, analyse de prot´

eines, g´

enome

–traitement d’images

–analyse du langage parl´

e

•Limite physique `

a l’am´

elioration de la vitesse des circuits

1

Slide 3

2 Classification de Flynn

Classe les machines selon le nombre de flux de donn´

ees et d’instructions:

SISD =

Single Instruction stream, Single Data stream

: Uniprocesseur classique ex´

ecutant (du

point de vue du programmeur) une seule instruction `

a la fois, e.g., machine RISC moderne.

SIMD =

Single Instruction stream, Multiple Data streams

: Machine o`u une seule instruction

s’ex´

ecute sur plusieurs donn´

ees ind´

ependantes `

alafois.

MISD =

Multiple Instruction streams, Single Data stream

: Aucune machine connue.

MIMD =

Multiple Instruction streams, Multiple Data streams

: Plusieurs instructions distinctes

s’ex´

ecutant sur des donn´

ees ind´

ependantes.

Slide 4

3 Processeurs modernes et parall´

elisme

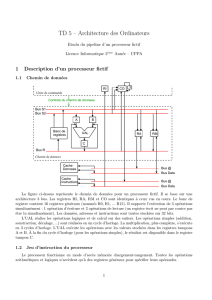

3.1 Pipeline d’analyse et d’ex´

ecution des instructions

•Plusieurs instructions cons´

ecutives peuvent ˆ

etre en cours d’ex´

ecution au mˆ

eme moment,

mais `

a des ´

etapes diff´

erentes

IF ID EX MEM WB

IF: Instruction Fetch

ID: Instruction Decode

EX: Execute

MEM: Memory Access

WB: Write Back

•Permet la r´

eduction du temps de cycle du processeur (augmentation de la fr´

equence de

l’horloge)

•Probl`

emes et solutions:

–Al´

eas de donn´

ees ⇒unit´

ede

forwarding

–Al´

eas de contrˆ

ole ⇒

pr´

ediction dynamique des branchements

2

Slide 5

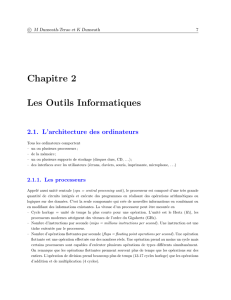

3.2 Machines superscalaireset ordonnancement dynamique des instruc-

tions

•Plusieursinstructionspeuvent ˆ

etre en cours d’ex´

ecutiondansdes unit´

esd’ex´

ecutiondiff´

erentes

(en autant que les d´

ependances de donn´

ees soient respect´

ees)

Station de

réservation Station de

réservation Station de

réservation Station de

réservation

Unité

entière

Unité

entière Unité

flottante chargement

Unité de

IF/ID

Unité de

mise à la

retraite

(Commit)

Émission

en ordre

Exécution

dans le

désordre

Mise à la

retraite

en ordre

. . .

. . .

Slide 6

3.3 Tampon d’´

ecriture et ex´

ecution pipelin´

ee des acc`

es m´

emoire

Ex´

ecution d’un store: Le processeur

amorce

l’ex´

ecution du store puis continue imm´

edia-

tement avec l’instruction suivante

⇒Plusieurs acc`

es m´

emoire en cours d’ex´

ecution

Processeur

Cache

Memoire

store $2, 100($6) ; Compl`

ete imm´

ediatement

store $4, 104($7) ; Compl`

ete imm´

ediatement

load $3, 104($7) ; Attente pour la valeur

3

Slide 7

4´

Evolution des architectures parall`

eles

4.1 Machine SIMD

PE PE PE PE

PE PE PE PE

PE PE PE PE

PE PE PE PE

Unité

de

contrôle

•Tr `

es courantes parmi les premi`

eres ma-

chines parall`

eles mais de moins en moins

usit´

e de nos jours.

•Typiquement des machines qui manipulent

des tableaux (matrices) de donn´

ees, con-

duisant `

a du “parall´

elisme de donn´

ees”.

VAR A, B, C: ARRAY[1..4, 1..4] OF REAL;

C:=A+B;

Slide 8

•Motivations initiales pour de telles machines:

–Obtenir une machine parall`

eledecoˆut faible endupliquant uniquement les unit´

esd’ex´

ecution

sans dupliquer l’unit´

e de contrˆ

ole.

–Minimiser l’espace m´

emoire requis en ayant une seule copie du code.

•D´

esavantage majeur: Excellent pour des programmes manipulant des tableaux uniformes

de donn´

ees,

mais

tr`

es difficile `

a programmer et `

a utiliser efficacement (les instructions

conditionnelles peuvent conduire un grand nombre de processeurs `

a rester inactifs).

Dernier exemple important (ann´

ees 80) d’une telle machine:

Connection Machine

, avec 64K

processeurs ... `

a 1 bit chacun

4

Slide 9

4.2 Machine MIMD avec bus et m´

emoire partag´

ee

Multiprocesseurs

CacheCache

Processeur Processeur

Mémoire

Avantages/d´

esavantages:

+Probl`

emedelacoh´

erence des caches facilement r´

esolu (

snoopy bus

)

−Ne permet pas le parall´

elisme massif (max. ≈30 processeurs) pcq.

1 seule

transaction `

a

la fois sur le bus

Slide 10

4.3 Machine MIMD avec r´

eseau et m´

emoire distribu´

ee

Multi-ordinateurs

Cache

Processeur

Cache

Processeur

MémoireMémoire

Réseau

Avantages/d´

esavantages:

+Permet un plus grand parall´

elisme (transactions multiples sur le r´

eseau)

=Probl`

emedelacoh´

erence des cache r´

esoluble mais plus complexe

−Temps de latence

impr´

evisible

(

NUMA = Non-Uniform Memory Access

)⇒Que faire en cas

de faute de cache/acc`

es r´

eseau?

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%