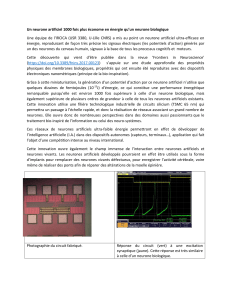

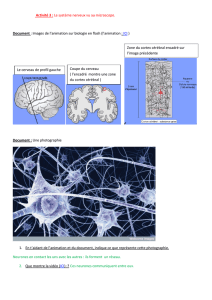

Neurones artificiels sur silicium : une évolution vers les réseaux.

publicité