eISP : processeur vidéo pour la téléphonie mobile

eISP

eISP : processeur vid

: processeur vidé

éo

o

pour la t

pour la té

él

lé

éphonie mobile

phonie mobile

Mathieu Thevenin, Laurent Letellier - CEA LIST

et Michel Paindavoine - Université de Bourgogne, LE2i

Dans le domaine des processeurs vidéo pour la téléphonie mobile, la demande en ressources de calcul à bas coût est forte notamment pour

traiter les standards vidéo haute-définition 720p et 1080p qui sont les futurs standards du marché pour ce type de dispositifs embarqués.

L’architecture eISP développée par le CEA LIST vise à supporter ces résolutions tout en proposant une solution programmable, basse

consommation et à faible empreinte silicium.

Fig. 1. Exemple de chaîne de traitement vidéo

Traitements

46%

Contrôle

16% Accès aux

données

38% Additions;

soustractions;

décalages;

accès aux registres.

Additions;

multiplications;

soustractions;

décalages;

accès à la mémoire;

accès aux registres.

Additions;

comparaison

s;

sauts;

accès aux registres.

10

10 à

à30

30 GOPs

GOPs

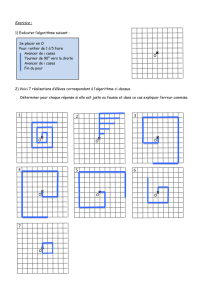

1 : Les algorithmes

1 : Les algorithmes à

àsupporter

supporter

(cf. Fig 1 et 2)

*HD 1080p : résolution 1920x1080 à 25 images par seconde soit 52MPx/s

Fig. 2. Répartition des tâches et des opérations

Results serialization

Input Output

Instructions

Pixel 1 & neighborhood access

Results

Channel

VLIW

#1

Program

Memory

Program

Counter

Insctruction

Contoller

Line buffer 1

Line buffer 2

Line buffer 3

Neighborhood

Controller

FSM

Neighborhood

controller

Control unit

Stream controller

Instructions

VLIW

#2 VLIW

#3 VLIW

#4 VLIW

#5 VLIW

#6

FETCH DECODE EXECUTE

Vers plan mémoire

- mémoire de travail;

- co-processeurs;

- contrôleur externe...

Données externes

- voisinages;

- processeurs;

- plan mémoire...

Mémoire programme

Registres partagés:

- vers les autres processeurs;

- vers des coprocesseurs;

- vers des composants externes...

Balance des blancs

Correction gamma Correction des

pixels défectueux Démosaïquage Accentuation

Tuile 1 Tuile 2 Tuile 3 Tuile 4

Balance des blancs

Correction gamma

Normalisation d’histogramme

Tuile 5

Conversion

espace couleur

Tuile 6

2 : L

2 : L’

’architecture eISP

architecture eISP (cf. Fig 3 et 4)

Seuls les cœurs de boucles sont décrits par le programmeur. Les

processeurs sont dédiés uniquement au calcul du traitement vidéo.

- Tuiles de calcul composées de processeurs VLIW 2 voies SplitWay

- Processeurs fonctionnant en mode Multi-SIMD ou SIMD

- Accès aux données transparent (gestionnaire de voisinage)

- Variation de la fréquence des tuiles

(adaptation de la capacité de calcul)

- Synchronisation entre les tuiles par bus TDMA & horloge pixel

- Enchaînement des tuiles programmable par bus TDMA

3 : R

3 : Ré

ésultats (en technologie TSMC 65nm)

sultats (en technologie TSMC 65nm)

(cf Fig 6)

Processeur VLIW 2 voies SplitWay (instance 24 bits):

- Deux opérations/cycle soit 500 MOPs à 250 MHz pour une

consommation électrique de 4mW (100 MOPs/mW)

- Surface inférieure à 8kGates (0,02mm² 65nm)

L’architecture eISP (instance de 6 tuiles de 6 processeurs intégrant

les mémoires) :

- 14,4 GOPs @ 200MHz pour moins 250mW (57 MOPs/mW)

- Surface en technologie 65 nm : 1,5mm²

- Possibilité de traiter des voisinages 5x5

Fig. 3. Processeur SplitWay

VLIW 2 voies

Fig. 4. (en haut) Tuile de calcul SIMD composée de 6 processeurs VLIW SplitWay

Fig 5. (en bas) Chaîne de traitement telle qu’elle peut être portée sur eISP

Fig. 6. Layout d’une tuile

De calcul Multi-SIMD

L’architecture eISP, adaptée aux contraintes de l’embarqué, est capable de traiter des flux vidéo HD 1080p. Le processeur SplitWay,

spécialement conçu, lui confère une capacité de 57 MOPs par mW, ce qui la classe parmi les plus efficaces du marché. Sa structure en tuile

de calcul qui la rend scalable et son entière programmabilité permettent une utilisation d’eISP dans différents domaines d’application.

Suppression Normalisation

histogramme

quage

Accentuation

des contours

Etage de sortie

Capture Correction

de la dynamique Suppression

des bruits Correction

gamma

Balance des

blancs

DémosaïquageAccentuation

Les traitements de la chaîne d’amélioration vidéo sont

analysés pour du HD 1080p* ( 10 à 30 GOPs) :

-Identification et séparation des tâches

-Identification des opérateurs élémentaires

-Identification des niveaux de parallélisme exploitables

- Tâches Pipeline & tâches en temps masqué

- Instruction VLIW ( 2 voies)

- Spatial SIMD Multi-SIMD

1

/

1

100%

![III - 1 - Structure de [2-NH2-5-Cl-C5H3NH]H2PO4](http://s1.studylibfr.com/store/data/001350928_1-6336ead36171de9b56ffcacd7d3acd1d-300x300.png)