Etude et réalisation d`un circuit intégré spécifique de mise en forme

Etude et r´ealisation d’un circuit int´egr´e sp´ecifique de

mise en forme de signaux d´elivr´es par un d´etecteur pour

une exp´erience de physique des particules

Laurent Royer

To cite this version:

Laurent Royer. Etude et r´ealisation d’un circuit int´egr´e sp´ecifique de mise en forme de signaux

d´elivr´es par un d´etecteur pour une exp´erience de physique des particules. Physique des Hautes

Energies - Exp´erience [hep-ex]. Conservatoire national des arts et metiers - CNAM, 2001.

Fran¸cais.

HAL Id: tel-00001313

https://tel.archives-ouvertes.fr/tel-00001313

Submitted on 16 Apr 2002

HAL is a multi-disciplinary open access

archive for the deposit and dissemination of sci-

entific research documents, whether they are pub-

lished or not. The documents may come from

teaching and research institutions in France or

abroad, or from public or private research centers.

L’archive ouverte pluridisciplinaire HAL, est

destin´ee au d´epˆot et `a la diffusion de documents

scientifiques de niveau recherche, publi´es ou non,

´emanant des ´etablissements d’enseignement et de

recherche fran¸cais ou ´etrangers, des laboratoires

publics ou priv´es.

CONSERVATOIRE NATIONAL DES ARTS ET METIERS

CENTRE REGIONAL ASSOCIE DE CLERMONT-FERRAND

_________

MEMOIRE

présenté en vue d’obtenir le

DIPLOME D’INGENIEUR C.N.A.M.

en

ELECTRONIQUE

par

Laurent ROYER

Etude et réalisation d’un circuit intégré spécifique

de mise en forme de signaux délivrés par un détecteur

pour une expérience de Physique des particules

Soutenu le 11 mai 2001

JURY :

Président : Monsieur H. VU THIEN

Membres : Monsieur A. BALDIT

Monsieur J.P. BLANC

Monsieur G. BOHNER

Monsieur J.P. CHAUSSE

Monsieur Y. CUMINAL

Monsieur M. SCHNEIDER

Monsieur R. VALLET

Les particules sont les graines du jardin qu'est notre Univers

Gordon Kane

Remerciements

Je voudrais tout d'abord remercier les membres du Jury, et notamment son

Président Monsieur Vu Thien, professeur au Conservatoire National des Arts et

Métiers de Paris, d'avoir accepté de bien vouloir juger le travail présenté dans ce

mémoire.

Je remercie Monsieur Jean-Pierre Chausse d'avoir accepté de suivre mon travail

en sa qualité de responsable de la filière électronique du Centre Régional Associé au

CNAM de Clermont-Ferrand.

Ce stage s'est déroulé au sein de l'équipe d'électronique du Laboratoire de

Physique Corpusculaire de Clermont-Ferrand, équipe à laquelle j'appartiens depuis

janvier 1998. Je remercie vivement Monsieur Bernard Michel, Directeur du LPC, et

Monsieur Michel Brossard, responsable de l'équipe d'électronique, d'avoir mis tous les

moyens nécessaires à ma disposition pour travailler dans les meilleures conditions

possibles. Qu'ils soient par la même occasion remerciés pour leur soutien à la formation

permanente de leurs personnels techniques.

J'exprime toute ma reconnaissance à Monsieur Gérard Bohner qui, durant toute

la durée du stage et de la rédaction de ce mémoire, m'a guidé et fait partagé ses

connaissances et son expérience de la micro-électronique dédiée aux expériences de

Physique des particules. Ces remerciements peuvent d'ailleurs être étendus à l'ensemble

du groupe de micro-électronique du LPC dirigé par Monsieur Jacques Lecoq.

Je tiens à remercier les membres de l'équipe clermontoise travaillant sur le projet

ALICE, et notamment leurs responsables, Monsieur Alain Baldit et Monsieur Pascal

Dupieux, qui m'ont fourni un sujet particulièrement intéressant et motivant.

D'une manière générale, je remercie tous ceux qui ont bien voulu porter un œil

critique à mon travail.

Enfin, je voudrais exprimer toute ma reconnaissance à ma femme qui n'a cessé

de m'encourager et de me soutenir durant ces dix années de formation suivie à Nice et

Clermont-Ferrand.

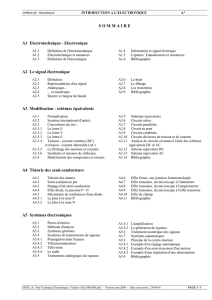

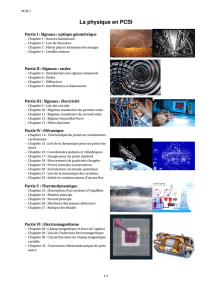

Table des matières

Introduction 1

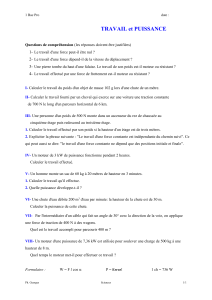

1 Rôle du circuit frontal 3

1.1 La Physique de l'expérience ALICE..................... 3

1.1.1 L'expérience ALICE au CERN.................... 3

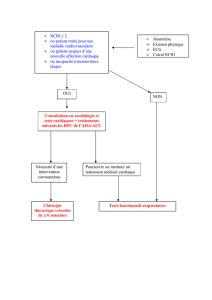

1.1.2 Le système de déclenchement du Spectromètre Dimuons.... 4

1.1.3 Les détecteurs RPC............................. 6

1.1.4 Les deux modes de fonctionnement................ 7

1.2 L'électronique frontale des détecteurs RPC............... 11

1.2.1 L'électronique frontale initiale.................... 12

1.2.2 Le système ADULT........................... 13

1.2.3 Autres fonctions requises....................... 16

2 Etude et conception du circuit intégré spécifique 17

2.1 Pré-étude....................................... 17

2.1.1 Le cahier des charges.......................... 17

2.1.2 Une solution à base de composants génériques ....... 18

2.1.3 Une solution basée sur un circuit intégré pour application

spécifique (ASIC)............................ 19

2.2 Conception du circuit intégré spécifique................. 21

2.2.1 Description générale .......................... 21

2.2.2 Les cellules "COMPARATEUR"..................... 23

2.2.3 La cellule "BLOQUEUR"..........................35

2.2.4 La cellule "COINCIDENCE"........................ 39

2.2.5 Les cellules "DELAI", "VERROUILLAGE", "MISE EN FORME" et

"DELAI_VAR"................................. 41

2.2.6 L'étage de sortie du circuit...................... 46

2.2.7 La saisie des masques.......................... 48

3 Résultats des tests du circuit intégré 52

3.1 Introduction..................................... 52

3.2 Tests en laboratoire................................ 52

3.2.1 Les comparateurs et la fonction ADULT............ 52

3.2.2 Le système de verrouillage ...................... 55

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

1

/

106

100%