Rapport - mescal

1

CELL et SystemC

Apprentissage des outils d´

evelopp´

es dans le groupe

Alp KILIC

Rapport de Stage, Universit´

e Joseph Fourier, Magist`

ere 2006-2007

R´

esum ´

e—Chaque nouvelle g´

en´

eration de processeur d´

evelopp´

e cause encore des probl`

emes et rend difficile de choisir

la platforme qui convient mieux pour les domaines differentes. C’est impossible de faire des tests au niveau mat´

eriel pour

une usage pr´

ecis (Couteux et tr`

es lents). Les simulations au niveau logiciel donnent des reponses plus facilement mais

sans avoir une pr´

ecision exacte. Le but de ce stage est de comprendre l’architecture du processeur Cell et comprendre

aussi l’outil d´

evelopp´

es dans le groupe pour faire une simulation logiciel qui est assez bas niveau en SystemC.

F

1 INTRODUCTION

LAformation Magist`

ere nous offre la

possibilit´

e de voir le monde de la

recherche. Pour ce qui veut faire de la

recherche apr`

es ses ´

etudes, il est important

de connaitre la vie professionnelle et sociale

dans les laboratoires et savoir s’int´

egrer dans

le groupe de recherche. Le laboratoire TIMA

a une longue exp´

erience sur la conception de

mat´

eriel et sur les logiciels CAD. Il se concentre

sur de divers aspects de la conception, CAD,

test de circuits et de syst`

emes.

Le monde du mat´

eriel informatique reste

toujours la partie obscure pour la plupart des

informaticiens. Cependant il se d´

eveloppe tr`

es

rapidement et n´

ecessite un travail s´

erieux.

Nous allons aborder le probl`

eme de faire la

simulation des mat´

eriaux au niveau logiciel.

Pour cela on va d’abord examiner l’architecture

de CELL qui est un processeur assez r´

ecent et

populaire. Apr`

es on va faire la connaissance

avec l’extension du langage de programmation

C++ pour faire la simulation mat´

eriel :

SystemC.

2 CELL

Cell est une architecture de microprocesseur

conjointement d´

evelopp´

ee par Sony, Toshiba et

IBM (une alliance nomm´

ee STI).La conception

architecturale et la premi`

ere ex´

ecution ont ´

et´

e

effectu´

ees au centre de STI sur une p´

eriode de

4 ans commenc¸ant en mars 2001.

Il est conc¸u pour ´

etablir le lien entre les

processeurs de bureau conventionnels (tels

que les familles bien connues de Pentium et

de PowerPC) et les processeurs sp´

ecialis´

es en

terme de graphique comme les processeurs de

nVIDIA ou d’ATI (GPUs). Il peut ˆ

etre utilis´

e

dans les domaines de l’application multim´

edia,

les simulations physiques, l’imagerie m´

edicale

etc.

La premi`

ere application commerciale

principale du Cell ´

etait dans la console

de jeu de PlayStation 3 de Sony.

Cell peut ˆ

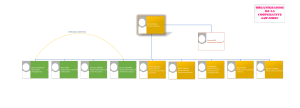

etre examin´

e en quatre principaux

composants : les contrˆ

oleurs d’entr´

ee/sortie

et de m´

emoire, le processeur principal

«Power Processing Element »(PPE), huit co-

processeurs appel´

es «Synergistic Processing

Elements »(SPEs), et un bus de donn´

ees en

anneau qui relie les autres composants entre

eux appel ´

e«Element Interconnect Bus »

(EIB).

Afin d’avoir le rendement ´

elev´

e pour pouvoir

faire des calculs assez compliqu´

e comme le

codage ou le d´

ecodage de la vid´

eo (MPEG),

Cell relie simplement les SPEs et le PPE grˆ

ace

2

a EIB. Le PPE qui est capable d’exploiter

un syst`

eme d’exploitation, a le contrˆ

ole du

SPEs et peut commencer, arrˆ

eter, interrompre

et programmer des processus fonctionnant

sur les SPEs. C’est pour cela le PPE poss`

ede

des instructions additionnelles concernant

la commande du SPEs. La vraie puissance

du Cell vient de ses fameux «Synergistic

Processing Elements »

On peut voir en details les quatres principaux

parties du Cell :

2.1 PPE

PPE est un coeur bi-directionnel multitache

bas´

ee `

a ”Power Architecture” agissant en tant

que contrˆ

oleur pour les SPEs qui manipulent

la majeure partie du travail de calcul. PPE

peut fonctionner avec les syst`

emes d’exploita-

tion conventionnels dus `

a sa similitude d’autres

processeurs 64-bit PowerPC, alors que SPEs

sont conc¸us pour faire des calculs vectoriels.

2.2 SPEs

Chaque SPE est compos´

e de Synergistic

Processing Unit SPU, un cotrˆ

oleur m´

emoire

Memory Flow Controller MFC et une m´

emoire

locale Local Store LS.

SPE op`

ere une m´

emoire locale (256 Ko) qui

stocke des instructions et des donn´

ees. Des

donn´

ees et les instructions sont transf´

er´

ees

entre cette m´

emoire locale et la memoire

centrale par des commandes asynchrones de

DMA, ex´

ecut´

ees par MFC inclus dans chaque

SPE.

Un seul SPE peut operer 16 entiers 8 bits, 8

entiers 16 bits, 4 entiers 32 bits ou 4 floats de

pr´

ecision simple dans un seul cycle d’horloge.

Il peut aussi faire des operations de m´

emoire

dans le meme cycle. Il n’a pas d’acces direct `

a

la m´

emoire centrale. Les adresses de m´

emoire

64-bits constitu´

ees par SPU doivent ˆ

etre

pass´

ees du processeur de SPU au cotrˆ

oleur

m´

emoire MFC pour pr´

eparer une op´

eration

de DMA dans l’espace adresse de syst`

eme.

2.3 EIB

EIB est le coeur de l’architecture de

la communication du Cell. Il permet la

communication entre PPE, SPEs, la m´

emoire

centrale et les entr´

ees/sorties externes.

EIB est compos´

e de 4 anneaux des donn´

ees de

16 octets : deux fonctionnant dans le sens des

aiguilles d’une montre, et les deux autres dans

le sens contraire des aiguilles d’une montre.

Chaque anneau permet potentiellement jusqu’`

a

trois transferts de donn´

ees concourants jusqu’`

a

ce que leurs chemins ne recouvrent pas.

Pour lancer un transfert de donn´

ees, les

´

el´

ements de bus doivent demander l’acc`

es de

bus de donn´

ees.L’arbitre de bus de donn´

ees

de EIB traite ces demandes et d´

ecide quel

anneau devrait manipuler. L’arbitre choisit

toujours un des deux anneaux qui a le chemin

le plus court dans la direction du transfert, de

ce fait s’assurant que les donn´

ees n’auront pas

besoin de faire plus qu’`

a mi-chemin autour de

l’anneau `

a sa destination.

Pour r´

eduire au minimum la perte de vitesse,

l’arbitre accorde la priorit´

e aux demandes

venant du contrˆ

oleur de m´

emoire.

EIB fonctionne `

a la moiti´

e vitesse de l’horloge

du processeur. Chaque unit´

e de EIB peut

simultan´

ement envoyer et recevoir 16 octets

de donn´

ees dans chaque cycle de bus.

2.4 Contr ˆ

oleurs I/O et m´

emoires

Le MIC est un double contrˆ

oleur m´

emoire

XDR (XDRAM) offrant un d´

ebit de 25,6 Go

par seconde. On trouve deux interfaces E/S

configurables (76,8 Go/s, 6,4 Gbit/s) (Flexible

I/O).

3

3 SYSTEMC

SystemC n’est qu’une biblioth`

eque de

classe de C++ particuli`

erement conc¸ue pour

la conception de syst`

eme. Conservant les

fonctionnalit´

es du C++, il reste possible de

d´

ecrire des fonctions purement logicielles.

SystemC permet donc de mod´

eliser des

syst`

emes mat´

eriels, logiciels, mixtes ou mˆ

eme

non-partitionn´

es.

SystemC remplace HDL comme Verilog

et VHDL dans beaucoup de situations. Ceci

ne signifie pas que ces HDL ne sont plus

utiles. Mais le systemC soutient une nouvelle

approche pour concevoir un syst`

eme.

Pourquoi l’utiliser ?

SystemC est n´

ee en raison des n´

ecessit´

es de

l’industrie ´

electronique actuelle : Aujourd’hui,

Les instruments ´

electroniques se d´

eveloppent

tr`

es rapidement sans avoir compte du temps

de se produire et se lancer sur le march´

e. Il

n’est vraiment pas facile pour les ing´

enieurs de

concevoir un nouveau syst`

eme. La complexit´

e

des nouvelles technologies rend la situation

encore plus difficile. Pr´

ec´

edemment, le C (ou

C++) a ´

et´

e utilis´

e pour ´

ecrire la partie logiciel

de la conception. Pour le mat´

eriel, c’´

etait

du HDL. Il ´

etait tr`

es difficile d’installer un

«testbench »qui est commun pour tous les

deux, puisqu’ils sont des langages enti`

erement

diff´

erents. L’introduction du SystemC a r´

esolu

la plus part de ces probl`

emes.

Les Avantages de SystemC :

– Il h´

erite de tous les traits de C++, qui

est un langage de programmation stable

admis partout dans le monde.

– Riches dans les types de donn´

ees : Avec

les types soutenus par C++, SystemC

soutient l’utilisation des types de donn´

ees

sp´

eciaux qui sont souvent utilis´

es par les

concepteurs de mat´

eriel

– Il a un noyau de simulation qui est tres

fort pour permettre aux concepteurs

de faire des tests et des simulations

dessus. C’est assez important parce que

la v´

erification fonctionnelle au niveau de

syst`

eme ´

economise beaucoup d’argent et

de temps.

– Il int`

egre la notion du temps `

a C++ pour

simuler des conceptions synchrones de

mat´

eriel.

– SystemC soutient la conception a un

niveau plus ´

elev´

e d’abstraction, tandis

que la majeure partie des «HDL »

soutient le RTL (Register transfer level )

de la conception.

– Simultan´

eit´

e : Pour simuler le

comportement simultan´

e.

4 CONCLUSION

La simulation logicielle nous donne l’oppor-

tunit´

e de tester facilement des syst`

emes tres

complexe comme «CELL ». Pour avoir des

r´

esultats plus fins il suffit d’am´

eliorer cette

m´

ethode. Ce stage n’´

etait que l’apprentissage

de ces m´

ethodes. J’esp`

ere de continuer `

a faire

des exp´

erimentations sur le sujet.

1

/

3

100%