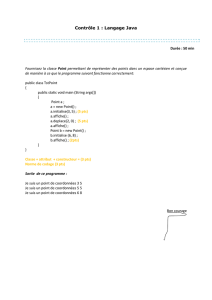

Examen d`architecture des ordinateurs

Examen!d'architecture+des+ordinateurs!

1IN,%21%janvier%2013%–%2h%

!

!

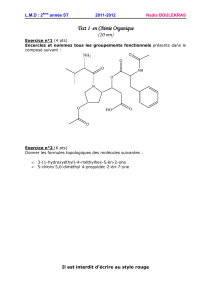

1. Arithmétique--(2-pts)-

"#$%&!%'!%((%)'*%&!+%$!#,-&.'/#0$!$*/1.0'%$2!%0!.&/'34-'/5*%!$/60-%!$*&!7!8/'$!9!

:;<<=>!;!:?=7>!!!!!@!!!:?AB>!;!:?CD>!

E0F/5*%&!F.0$!)3.5*%!).$!$G/+!H!.!F-8#&F%4%0'!%'!%I,+/5*%&!,#*&5*#/J!

2. Logique-combinatoire--(3-pts)-

K.0$!*0%!8.05*%2!A!%4,+#H-$!#0'!.))L$!.*!)#((&%?(#&'!:MN>J!M%$!A!%4,+#H-$!O2!P2!M!%'!K!,#$$LF%0'!

)3.)*0!*0%!)+-!F/((-&%0'%!4./$!.*)*0!0%!,%*'!#*1&/&!+%!)#((&%?(#&'!'#*'!$%*+J!

• QG%4,+#H-!O!.!8%$#/0!5*%!+G%4,+#H-!P!$#/'!,&-$%0'J!

• Q%$!%4,+#H-$!P!%'!M!#0'!8%$#/0!5*G.*!4#/0$!F%*I!.*'&%$!%4,+#H-$!$#/%0'!,&-$%0'$J!

• QG%4,+#H-!K!0%!,%*'!#*1&/&!5*G%0!,&-$%0)%!F%!'#*$!+%$!.*'&%$!%4,+#H-$J!

!

<J K&%$$%&!+.!'.8+%!F%!1-&/'-!F%!+.!$#&'/%!MN!:%0!(#0)'/#0!F%$!%0'&-%$!O2P2M2K>2!5*/!1.*'!<!+#&$5*%!

+%!)#((&%?(#&'!%$'!#*1%&'!%'!R!$/0#0!

SJ T&#*1%&!*0%!%I,&%$$/#0!F%!MN!6&U)%!V!*0%!'.8+%!F%!W.&0.*63!

DJ X)&/&%!+%!4#F*+%!YZKQ!coffrefort(A, B, C, D : CF)!)#&&%$,#0F.0'!

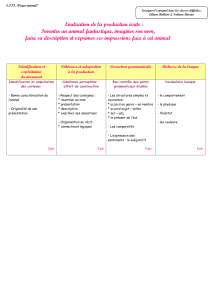

3. Circuit-séquentiel-–-synthèse-fonctionnelle-(4-pts)-

M#0)%1#/&!*0%!,/+%!4.'-&/%++%!F%!A!4#'$!F%!DS!8/'$2!.1%)!+[/0'%&(.)%!$*/1.0'!9!

!

• +#&$5*%!%0\R2!5*%++%!5*%!$#/'!+.!1.+%*&!F%!)4F2!+[-'.'!F%!+.!,/+%!0%!)3.06%!,.$!.*!(�'!

F[3#&+#6%!

• Q#&$5*%!)4F\<!:,*$3>!%'!%0\<2!+.!F#00-%!F.'.E0!%$'!%4,/+-%!.*!(�'!F[3#&+#6%!

• F.'.]*'!(#*&0/'!'#*^#*&$!+.!F%&0/L&%!1.+%*&!%4,/+-%!

• +#&$5*%!)4F\R!:,#,>!%'!%0\<2!+%!4#'!4-4#/&%!.*!$#44%'!F%!+.!,/+%!%$'!&%'/&-!

• #0!0%!6-&%&.!,.$!+%$!$/'*.'/#0$!F%!,#,!+#&$5*%!+.!,/+%!%$'!1/F%!#*!F%!,*$3!+#&$5*%!+.!,/+%!%$'!

,+%/0%!

K%$$/0%&!+%!$)3-4.!F*!4#F*+%J!]0!,#*&&.!*'/+/$%&!F%$!&%6/$'&%$!DS!8/'$!.1%)!%0.8+%!%'!F%$!

4*+'/,+%I%*&$!DS!8/'$!9!

!

!

!

in out

clk

ena

32 32

32

32

32

0

1

sel

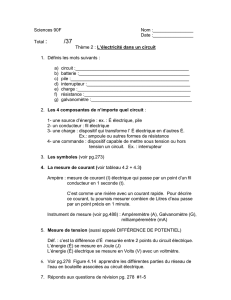

4. Circuit-séquentiel-–-graphe-d’états-(4-pt)-

]0!1%*'!)#0)%1#/&!*0!)/&)*/'!$-5*%0'/%+!5*/!F-)+%0)3%!*0!$/60.+!F[.&&_'!+#&$5*[#0!.)'/1%!*0%!%0'&-%!

F%!F%4.0F%!F[.&&_'!F*&.0'!*0%!$%)#0F%J!Q[/0'%&(.)%!F*!)/&)*/'!$%&.!9!

!module circuit_arret(rst, h, dem : arret)

On#utilise#une#horloge#à#1Hz,#de#sorte#qu’il#suffit#que#la#commande#d’arrêt#dem!$#/'!,&-$%0'%!F*&.0'!

F%*I!(�'$!:4#0'.0'$>!F[3#&+#6%!)#0$-)*'/($!,#*&!F-)+%0)3%&!+[.&&_'J!`0%!(#/$!+%!$/60.+!arret!

activé,(il(ne(peut(plus(_'&%!F-$.)'/1-!:$.*(!+#&$!F[*0!&%$%'>J!

!

M#0)%1#/&!)%''%!&-.+/$.'/#0!$#*$!(#&4%!F[*0!)/&)*/'!$-5*%0'/%+!$H0)3�%!,*&!F%!'H,%!a]]bcJ!N#*&0/&!

+%!6&.,3%!F[-'.'$!%'!+%$!-5*.'/#0$!YZKQ!F*!)/&)*/'J!

5. CRAPS-:-programation-(3-pts)-

X)&/&%!+%!$#*$?,&.44%!5*/!).+)*+%!+%!4.I/4*4!FG*0!'.8+%.*!FG%0'/%&$!$/60-$!:&%+.'/($>!F#0'!

+G.F&%$$%!%'!+.!'./++%!$#0'!,.$$-%$!%0!,.&.4L'&%J!

• /0F/5*%&!)+./&%4%0'!1#$!)3#/I!%0!'%&4%!F%!,.$$.6%!F%$!,.&.4L'&%$!%'!F*!&-$*+'.'!

• 5*%+!)3.06%4%0'!%((%)'*%&!$/!+%!'.8+%.*!%$'!)#0$'/'*-!FG%0'/%&$!0.'*&%+$!:,#$/'/($>!d!

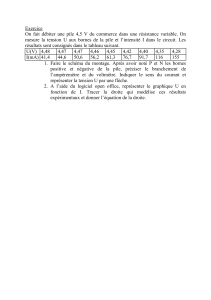

6. CRAPS-:-ajout-d’une-instruction-(5-pts)-

]0!$#*3./'%!.^#*'%&!.*!,&#)%$$%*&!MbO"Y!*0!.*'&%!6&#*,%!FG/0$'&*)'/#0$!F*!'H,%!9!

opération)arithmétique// rs,/[rad1+rad2]/

#e!+G#,-&.'/#0!.&/'34-'/5*%!%$'!&-.+/$-%!%0'&%!+%!&%6/$'&%!&$!%'!+%!4#'!4-4#/&%!F#0'!+G.F&%$$%!%$'!

-6.+%!V!&.F<;&.FS2!%'!$'#)f%!+%!&-$*+'.'!F.0$!+%!4_4%!4#'!4-4#/&%J!

]0!,#*&&.!-)&/&%!%0!.$$%48+%*&!,.&!%I%4,+%!9!

subcc %r1, [%r5+%r7]

M%''%!/0$'&*)'/#0!+/&.!+%!4#'!4-4#/&%!!F%!)#0'%0*!a!$/'*-!V!+[.F&%$$%!O\g&B;g&=2!%((%)'*%&.!

+[#,-&.'/#0!g&<!h!a2!%'!$'#)f%&.!+%!&-$*+'.'!%0!4-4#/&%!V!+[.F&%$$%!OJ!

M%!6&#*,%!FG/0$'&*)'/#0$!.!,#*&!(#&4.'!9! !

!

• K.0$!5*%+:$>!4#F*+%:$>!%((%)'*%&!)%$!4#F/(/).'/#0$!d!Q%$!F-'./++%&!

h

dem

a

rret

• i*%+!6./0!&-.+/$%?'?#0!:%0!g>!,.&!&.,,#&'!V!+.!4_4%!#,-&.'/#0!&-.+/$-%!.1%)!F%$!/0$'&*)'/#0$!

MbO"Y!)+.$$/5*%$!d!

1

/

4

100%