Allocation de mémoire dynamique dans les systèmes - Lab

MajecSTIC 2010

Bordeaux, France, du 13 au 15 octobre 2010

Allocation de mémoire dynamique dans les systèmes embarqués

María Soto, André Rossi et Marc Sevaux

Université de Bretagne-Sud, Lab-STICC,CNRS, Centre de recherche BP 92116,F-56321 Lorient

Cedex, France.

Contact : [email protected]

Résumé

Les concepteurs de circuits souhaitent trouver un compromis entre le coût de l’architecture et la

consommation électrique. La gestion de la mémoire cache a un impact significatif sur les perfor-

mances et sur la consommation énergétique des systèmes embarqués. Cet article traite de l’allo-

cation de mémoire des structures de données d’une application à la mémoire cache de manière

à optimiser les performances du système. Dans le problème abordé le temps est découpé en in-

tervalles de temps de durées différentes. Au cours de chaque intervalle de temps, l’application a

besoin d’accéder à un sous ensemble connu de structures de données. Contrairement à d’autres

versions du problème où l’on recherche une allocation statique valable pendant toute l’exécution

de l’application, on s’autorise à changer l’allocation des structures de données au cours de chaque

intervalle de temps en fonction des besoins de l’application. Le succès des métaheuristiques pour

des versions proches du problème suggèrent naturellement d’adapter ces méthodes au problème

d’allocation dynamique de mémoire dans les systèmes embarqués.

Mots-clés : Allocation de mémoire, Électronique, Recherche opérationnelle.

1. Introduction

La technologie en microélectronique a rendu possible le développement de circuits miniatures

permettant d’étendre considérablement les fonctionnalités des appareils multimédia portatifs (par

exemple la téléphonie mobile et le traitement d’images H.D). Alors que la technologie ouvre des

perspectives toujours plus larges, la conception des circuits intégrés devient, elle, de plus en plus

complexe. Cette évolution a rendu indispensable la conception de circuits par ordinateur, boule-

versant ainsi ce métier. Jusqu’alors, les circuit intégrés étaient conçus à la main par des spécialistes,

mais cette façon de faire n’est plus possible pour les circuits actuels. Les outils de conception as-

sistée par ordinateur comme Gaut [4] permettent de générer l’architecture d’un circuit intégré à

partir de ses spécifications, mais les solutions produites par ce biais souffrent généralement d’un

manque d’optimisation qui se traduit notamment par une consommation énergétique importante,

ce qui est particulièrement préjudiciable pour les systèmes embarqués.

Aussi les concepteurs de circuits cherchent-ils un compromis entre le coût de l’architecture (le

nombre de bancs mémoire à embarquer) et la consommation énergétique de l’ensemble [2]. Gé-

néralement, les électroniciens considèrent que dans une certaine mesure, minimiser la consom-

mation est équivalent à minimiser le temps d’exécution de l’application [3]. De plus, la consom-

mation d’une architecture donnée peut également être estimée à l’aide d’un modèle empirique

comme dans [10]. Ainsi, cherche-t-on à paralléliser l’accès aux données de manière à minimiser le

temps total d’exécution de l’application, et par conséquent sa consommation.

Dans cet article nous abordons la problématique de l’optimisation d’allocation de mémoire cache

des processeurs embarqués. En effet, la gestion de la mémoire cache a un impact significatif sur les

performances et sur la consommation énergétique comme l’ont montré Wuytack et al. dans [17].

Dans la section suivante nous présentons formellement le problème d’allocation mémoire dyna-

mique et un exemple qui permet de mieux comprendre ce problème.

2

María Soto, André Rossi & Marc Sevaux

2. Problème d’allocation mémoire dynamique

Lors de la conception d’un circuit intégré pour un système embarqué (typiquement un décodeur

MPEG, un filtre numérique ou tout autre algorithme de traitement du signal et de l’image), l’appli-

cation à synthétiser est fournie sous la forme d’un code source écrit en langage C, et les structures

de données manipulées doivent être placées dans des bancs mémoire (il s’agit de la mémoire

cache du processeur qui exécute l’application).

Le temps est découpé en Tintervalles de temps de durées différentes. La durée de chaque inter-

valle de temps est définie et donnée pour l’application. Au cours de chaque intervalle de temps,

l’application a besoin d’accéder à un sous ensemble connu de structure de données.

Contrairement à d’autres versions du problème comme par exemple [14] où l’on recherche une

allocation statique valable pendant toute l’exécution de l’application, on s’autorise à changer l’al-

location des structures de données au cours de chaque intervalle de temps en fonction des besoins

de l’application.

Généralement, les systèmes embarqués ont différents niveaux de bancs mémoire. Pour des raisons

technologiques comme pour des raisons de coût, le nombre de bancs mémoire et leurs capacités

sont limités dans chaque niveau. Les capacités des bancs mémoire dans les niveaux supérieurs

sont plus grandes que dans les niveaux inférieurs. Au contraire, le nombre des bancs mémoire

dans les niveaux inférieurs est plus grand que dans les niveaux supérieurs. Dans ce travail nous

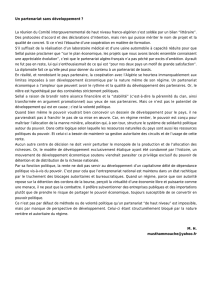

considérons deux niveaux de bancs mémoire comme le montre la figure 1. Le premier niveau a m

bancs mémoire {MB1,...,MBm}dont la capacité est c1, et le niveau supérieur est constitué d’un

seul banc mémoire MBm+1, lequel a une grande capacité c2(c’est-à-dire une capacité suffisante

pour allouer toutes les structures de données) et qui est appelée mémoire externe. Les tailles

mémoire sont exprimées en kilo octets (KO).

FIGURE 1 – Schéma de Dy-MemExplorer.

Le processeur doit accéder aux structures de données pour exécuter les opérations de l’appli-

cation. Une opération implique une ou plusieurs structures de données. Le temps d’accès aux

structures de données est mesuré en millisecondes. Ce temps d’accès dépend du niveau où les

structures de données sont allouées. Ainsi, le processeur dépense plus de temps pour accéder

aux structures de données qui se trouvent dans les bancs mémoire du niveau supérieur que pour

accéder aux structures du niveau inférieur. La figure 1 indique que le temps pour accéder aux

bancs mémoire du premier niveau est égal à une milliseconde et que le temps pour accéder aux

structures de données du niveau supérieur est égal à pmillisecondes.

Initialement (au cours de l’intervalle de temps 0), toutes les structures de données se trouvent

dans la mémoire externe. Le temps nécessaire au déplacement des structures de données de la

mémoire externe vers un banc mémoire du premier niveau ou vice-versa est égal à vmillise-

condes. Le temps nécessaire au déplacement des structures de données dans des bancs mémoire

du premier niveau est égal à lmilliseconde, comme le montre la figure 1. On suppose que dans

Allocation de mémoire dynamique

3

l’architecture du système il y a un contrôleur DMA (Direct Memory Access) qui permet l’accès di-

rect aux structures de données des bancs mémoire, alors les temps d’accès générés par ce contrôl-

leur sont modélisés par les paramètres vet l. Ainsi, le temps de déplacement des structures de

données est inférieur à leur temps d’accès (v < p).

On fait l’hypothèse que le processeur est capable d’accéder à tous ses bancs mémoire simulta-

nément, ce qui autorise plusieurs chargements en parallèle. Ainsi, les structures de données (ou

plus simplement les variables) aet bpeuvent être chargées en même temps lorsqu’on souhaite

effectuer l’opération a+b, à condition que aet bse trouvent dans deux bancs mémoire différents.

Si ces variables partagent le même banc mémoire, le processeur ne peut y accéder que séquentiel-

lement, ce qui nécessite deux fois plus de temps qu’un accès en parallèle. On dira que aet bsont

en conflit si elles apparaissent dans la même opération.

Tout conflit a un coût, qui est égal au nombre de fois où aet bapparaissent dans une même opé-

ration au cours de l’intervalle de temps considéré ; ce coût peut être un réel, dans le cas où le code

a été « profilé » par un outil logiciel [9, 11] basé sur une estimation stochastique de la probabilité

de branchement des instructions conditionnelles. Le recours à une estimation du nombre de fois

où une opération est effectuée se présente lorsque l’opération apparaît dans une boucle while ou

une instruction conditionelle if,else if par exemple.

Un conflit entre deux structures de données sera dit ouvert si les deux structures de données par-

tagent le même banc mémoire, il est dit fermé si les deux structures de données ont été affectées à

deux bancs mémoire différents.

Il faut noter qu’une structure de données peut être en conflit avec elle-même. Le cas se produit ty-

piquement lorsque la structure de données est un tableau et que l’application traduit une relation

de récurrence comme a[i] = a[i+1].

Le problème de l’allocation de mémoire est appelé Dy-MemExplorer et peut être formulé ainsi : al-

louer un banc mémoire à toute structure de données de l’application à chaque intervalle de temps,

de manière à minimiser le temps total d’accès aux données pour le processeur en respectant la ca-

pacité des bancs mémoire.

Dans cet article, on fait l’hypothèse que l’applicacion et ses données sont connues. En pratique, un

outil logiciel comme SoftExplorer peut produire ces données pour une application donnée, mais

les aspects relevant de l’analyse du code de l’application débordent le cadre de ce travail.

Dans le paragraphe qui suit, on propose un programme linéaire en nombres entiers (PLNE) pour

résoudre ce problème de manière exacte.

2.1. Modélisation du problème par PLNE

Soit nle nombre de structures de données de l’application et ntle nombre de structures de don-

nées auxquelles l’application doit accéder dans l’intervalle de temps tpour tout tdans {1...,T}.

Ainsi, PT

t=1nt≥n. On désigne par ai,t une structure de données dans l’intervalle tpour tout

i∈{1,...,nt}et t∈{1, . . . , T}. Par ailleurs, on note eai,t ,t le nombre d’accès à la structure de don-

nées ai,t dans l’intervalle t. On note otle nombre de conflits dans l’intervalle t. Finalement, on

définit dk,t le coût d’un conflit (k, t) = (ak1,t, ak2,t)dans l’intervalle tpour tout kdans {1,...,ot}

et tdans {1,...,T}.

Toutes ces informations sont considérées comme des données fournies par le concepteur (ou plus

exactement par un outil de profiling du code de l’application). L’architecture est décrite par les

temps d’accès aux bancs mémoire pet v, le nombre des niveaux et des bancs mémoire, les ca-

pacités des bancs mémoire et les tailles des structures de données, si. Les nombres d’accès aux

structures de données, la liste des conflits et leur coût sont des informations qui caractérisent

l’application.

Les variables de décision du problème représentent l’affectation des structures de données aux

bancs mémoire dans les intervalles de temps. Ainsi, pour tout i∈{1,...,n},j∈{1,...,m+1}et

t∈{1,...,T},xi,j,t =1indique que la structure de données iest affectée au banc mémoire jdans

l’intervalle de temps t,xi,j,t =0si ce n’est pas le cas.

Trois types de variables d’état sont utilisées dans le problème :

– La variable yk,t indique le statut du conflit (k, t)dans l’intervalle de temps t. Ainsi, yk,t =1si

le conflit kdans l’intervalle test fermé, sinon yk,t =0.

– La variable booléenne wi,t prend la valeur 1 si et seulement si la structure de données ia été

4

María Soto, André Rossi & Marc Sevaux

déplacée dans un banc mémoire du premier niveau entre les intervalles de temps t−1et t, pour

tout idans {1,...,n}et pour tout tdans {1, . . . , T}.

– La variable booléenne w0

i,t =1prend la valeur 1 si et seulement si la structure de données ia

été déplacée dans la mémoire externe ou si une structure de données ide la mémoire externe a

été déplacée vers un autre banc mémoire entre les intervalles de temps t−1et t.

Le coût d’une solution (c’est à dire d’une affectation des structures de données aux bancs mé-

moire) est égal au temps total d’accès et de déplacement des structures de données dans des bancs

mémoire appropriés pour exécuter les opérations nécessaires dans chaque intervalle de temps. Le

coût d’une solution s’exprime comme suit :

f(X) =

T

X

t=1

hnt

X

i=1

m

X

j=1eai,t,t·xai,t,j,t+p

nt

X

i=1eai,t,t·xai,t,m+1,t+

n

X

i=1

si·(wi,t+v·w0

i,t)−

ot

X

k=1

yk,t·dk,ti.

(1)

Le premier terme de (1) indique le temps d’accès des structures de données dans des bancs mé-

moire, le deuxième terme est le coût d’accès des structures de données affectées à la mémoire

externe ; le troisième terme est le coût de déplacement des structures de données et le dernier

terme est la somme des coûts des conflits fermés.

Comme Pnt

i=1Pm+1

j=1eai,t,t ·xai,t,j,t=Pnt

i=1eai,t,test une valeur constante, il est équivalent

de minimiser :

f(X) =

T

X

t=1

h(p−1)

nt

X

i=1eai,t,t ·xai,t ,m+1,t+

n

X

i=1

si·(wi,t +v·w0

i,t) −

ot

X

k=1

yk,t ·dk,ti.(2)

Les contraintes suivantes doivent être satisfaites pour l’ensemble des conflits dans chaque inter-

valle de temps pour que la solution soit réalisable.

Premièrement,toute structure de données est affectée à un banc mémoire ou à la mémoire externe :

m+1

X

j=1

xi,j,t =1, ∀i∈{1,...,n},∀t∈{1, . . . , T}.(3)

Deuxièmement, la somme des tailles des structures de données d’un banc mémoire ne doit pas

dépasser sa capacité.

n

X

i=1

xi,j,t ·si≤cj,∀j∈{1, . . . , m},∀t∈{1,...,T}.(4)

Troisièmement, pour tout conflit (k, t) = (ak1,t, ak2,t)de l’ensemble des conflits dans l’intervalle

t, la variable yk,t doit avoir la valeur numérique appropriée 0 ou 1. Cela est assuré à l’aide de la

contrainte ci-dessous :

xak1,t,j,t +xak2,t ,j,t ≤2−yk,t,∀j∈{1,...,m+1},∀k∈{1, . . . , ot},∀t∈{1, . . . , T}.(5)

Quatrièmement, les variables wi,t et w0

i,t qui modélisent le déplacement des structures de don-

nées doivent avoir la valeur appropriée 0 ou 1. Cela est assuré à l’aide des contraintes ci-dessous :

xi,j,t−1+xi,g,t ≤1+wi,t,∀i∈{1,...,n},∀j6=g, j, g ∈{1,...,m},∀t∈{1,...,T},(6)

xi,m+1,t−1+xi,j,t ≤1+w0

i,t,∀i∈{1,...,n},∀j∈{1,...,m},∀t∈{1, . . . , T},(7)

xi,j,t−1+xi,m+1,t ≤1+w0

i,t,∀i∈{1,...,n},∀j∈{1,...,m},∀t∈{1, . . . , T}.(8)

On rappelle qu’au début de l’application toutes les structures de données sont dans la mémoire

externe, comme le montrent les équations suivantes :

xi,j,0 =0, ∀i∈{1,...,n},∀j∈{1,...,m},

xi,m+1,0 =1, ∀i∈{1,...,n}.

Allocation de mémoire dynamique

5

Cinquièmement, xi,j,t,yk,t et wi,t sont des variables binaires :

xi,j,t ∈{0, 1},∀i∈{1, . . . , n},∀j∈{1,...,m},∀t∈{1,...,T},(9)

wi,t ∈{0, 1},∀i∈{1, . . . , n},∀t∈{1,...,T},(10)

w0

i,t ∈{0, 1},∀i∈{1, . . . , n},∀t∈{1,...,T},(11)

yk,t ∈{0, 1},∀k∈{1,...,ot},∀t∈{1,...,T}.(12)

Finalement, les équations (2)-(12) constituent le programme linéaire en nombres entiers pour Dy-

MemExplorer. Ce programme linéaire en nombres entiers peut être résolu pour les petites ins-

tances à l’aide d’un outil tel que GLPK [7] ou Xpress-MP [1].

Le programme linéaire pour Dy-MemExplorer permet d’obtenir des solutions optimales pour le

problème d’allocation mémoire dynamique. Il épargne aux spécialistes de faire manuellement

l’allocation mémoire à la main et garantit l’optimalité de la solution retournée.

La génération des instances pour le problème Dy-MemExplorer n’est pas facile, parce qu’il est

nécessaire de connaître à chaque intervalle de temps les variables et le nombre d’accès associé.

Le laboratoire Lab-STICC développe actuellement des outils pour la génération d’instances pour

le problème Dy-MemExplorer. Dans le paragraphe suivant nous présentons une instance réelle

générée manuellement.

2.2. Exemple

On présente une instance de Dy-MemExplorer créée à partir du code du filtre LMS bi-voies [8,

16], qui est un algorithme connu pour le traitement de signal. Cet algorithme est programmé en

langage C et sur une cible TI C6201. De la compilation du code de l’algorithme nous obtenons une

instance constituée de huit structures de données dont la taille est égale à 16384 bits, deux bancs

mémoire de capacité égale à 32768 bits (32 KO). Le facteur pest égal à seize et les facteurs vet l

sont égaux à un. La table suivante montre pour chaque intervalle : les structures de données dont

l’application a besoin, le coût d’accès aux structures de données, les conflits et leurs coûts.

Intervalles Structures Conflits Coûts Coût d’accès

t=1,...,7 {a1,t,...,ant,t}(ak1,t, ak2,t)dk,t eai,t,t

1 { 1,5 } (1 ;5) 4095 e1,1 =e5,1 =4095

2 { 2,6} (2 ;6) 4095 e2,2 =e6,2 =4095

3 { 3,5 } (3 ;5) 4095 e3,3 =e5,3 =4095

4 { 4,6 } (4 ;6) 4095 e4,4 =e6,4 =4095

5 { 1,5,7} (1 ;7) 1 e1,5 =2

(1 ;5) 1 e5,5 =e7,5 =1

6 { 2,6,8 } (2 ;8) 1 e2,6 =2

(2 ;6) 1 e6,6 =e8,6 =1

7 { 3,4 } (3 ;3) 1 e3,7 =e4,7 =2

(4 ;4) 1

TABLE 1 – Example : LMS bi-voies

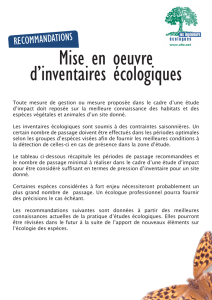

Une solution optimale trouvée par Xpress-MP [1] est illustrée par la figure 2. L’application dans

l’intervalle t=3doit lire la donnée 3. La solution consiste alors à échanger l’affectation des

données 1 et 3 pour éviter de lire la donnée 3 dans la mémoire externe. De la même façon à

l’intervalle t=4, les données 4 et 5 sont interchangées. Dans les derniers intervalles de temps

aucune structure de donnée ne change plus d’affectation. D’autre part, les données 7 et 8 sont

dans la mémoire externe pendant tout le temps d’execution de l’application, parce que leur coût

de déplacer est supérieur au coût d’accès. Ainsi elle minimise le temps d’accès aux structures

quand l’application exécute les opérations dans ces intervalles de temps.

6

6

7

7

1

/

7

100%