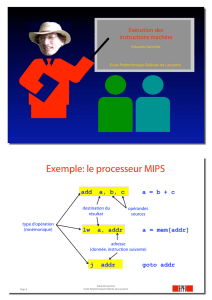

Les processeurs

Eduardo Sanchez

Laboratoire de Systèmes Logiques

Ecole Polytechnique Fédérale de Lausanne

Les processeurs

Eduardo Sanchez

Ecole Polytechnique Fédérale de Lausanne

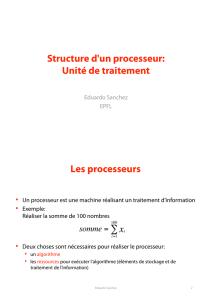

Les processeurs

uUn processeur est une machine réalisant un traitement

d’information

uExemple:

Réaliser la somme de 100 nombres

uDeux choses sont nécessaires pour réaliser le processeur:

Xun algorithme

Xles ressources pour exécuter l’algorithme (éléments de stockage et de

traitement de l’information)

somme

i

i

x

=

=

∑

1

100

Eduardo Sanchez

Ecole Polytechnique Fédérale de Lausanne

uL’algorithme pourrait être:

somme = 0

loop: for i=1 to 100

somme = somme + xi

end loop

Eduardo Sanchez

Ecole Polytechnique Fédérale de Lausanne

uLes ressources nécessaires pourraient être:

uLes signaux de contrôle des ressources (en rouge dans la

figure) sont générés par l’unité chargée d’exécuter l’algorithme

Xi 0

CK

Eduardo Sanchez

Ecole Polytechnique Fédérale de Lausanne

uUn processeur peut toujours être décomposé en deux parties:

Xl’unité de contrôle (chargée de l’exécution de l’algorithme)

Xl’unité de traitement (ensemble d’éléments de stockage et de

traitement de l’information)

uA chaque cycle d’horloge, l’unité de contrôle doit générer tous

les bits qui contrôlent les ressources de l’unité de traitement.

L’unité de contrôle est une machine séquentielle

unité

de

contrôle

unité

de

contrôle

unité

de

traitement

unité

de

traitement

entrées de contrôle entrées de données

sorties de contrôle sorties de données

signaux de contrôle

signaux de status

CK

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

1

/

31

100%