Structure d`un processeur: Unité de traitement Les processeurs

Structure d'un processeur:

Unité de traitement

Eduardo Sanchez

EPFL

Les processeurs

•Un processeur est une machine réalisant un traitement d’information

•Exemple:

Réaliser la somme de 100 nombres

•Deux choses sont nécessaires pour réaliser le processeur:

•un algorithme

•les ressources pour exécuter l’algorithme (éléments de stockage et de

traitement de l’information)

somme =

i

x

i=1

100

Eduardo Sanchez 2

•L’algorithme pourrait être:

somme = 0

loop: for i=1 to 100

somme = somme + xi

end loop

Eduardo Sanchez 3

•

Les ressources nécessaires pourraient être:

•Les signaux de contrôle des ressources (en rouge dans la gure)

sont générés par l’unité chargée d’exécuter l’algorithme

Xi 0

CK

Eduardo Sanchez 4

•

Un processeur peut toujours être décomposé en deux parties:

•

l’unité de contrôle (chargée du séquencement de l’algorithme)

•l’unité de traitement (ensemble d’éléments de stockage et de traitement de

l’information)

•A chaque cycle d’horloge, l’unité de contrôle doit générer tous les

bits qui contrôlent les ressources de l’unité de traitement.

L’unité de contrôle est une machine séquentielle

unité

de

contrôle

unité

de

traitement

entrées de contrôle entrées de données

sorties de contrôle sorties de données

signaux de contrôle

signaux de status

CK

reset

CK

reset

Eduardo Sanchez 5

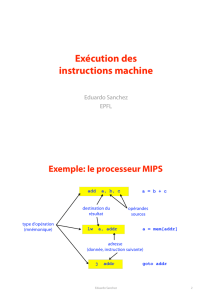

Exemple

•Concevoir un processeur capable de compter le nombre de 1

présents dans un mot d’entrée

•Un algorithme possible est:

data inport

ocount 0

mask 1

while data 0 repeat

temp data and mask

ocount ocount + temp

data data >> 1

end while

outport ocount

Eduardo Sanchez 6

•L’unité de traitement a besoin de 4 éléments de stockage, un par

variable de l’algorithme (data, mask, ocount, temp)

•La structure genérale du processeur serait donc:

unité

de

contrôle

unité

de

traitement

start inport

done outport

signaux de contrôle

data≠0

CK

reset

Eduardo Sanchez 7

Unité de traitement

•

Pour stocker les 4 variables de l’algorithme, on utilise un dispositif

avec 8 registres à double accès:

8 registres

CK

WA

WEN

RAA RAB

3

3 3

A B

Deux des 8 registres peuvent être lus en même temps, en donnant leurs adresses (RAA

et RAB).

On peut écrire sur le registre WA, en envoyant l’enable correspondant (WEN).

Les registres utilisés sont R1 (data), R2 (mask), R3 (ocount), R4 (temp) et R0 pour

stocker la constante 0

reset

Eduardo Sanchez 8

•

Pour les opérations sur les données nous utilisons une ALU et un

shifter:

shifter

A B

M

S

S

2

3

M S1 S0 ALU

0 0 0 A

0 0 1 A and B

0 1 0 A

B

0 1 1 A or B

1 0 0 A - 1

1 0 1 A + B

1 1 0 A - B

1 1 1 A + 1

S2 S1 S0 shifter

0 0 0 shift left

0 0 1 rotate left

0 1 0 shift right

0 1 1 rotate right

1 0 0 NOP

1 0 1 NOP

1 1 0 NOP

1 1 1 NOP

Eduardo Sanchez 9

8 registres

CK

WA

WEN

RAA RAB

3

3 3

A B

shifter

A B

M

S

SH

2

3

comparateur

1 0

outport

data≠0

0

inport

IE

OE

reset

Eduardo Sanchez 10

6

6

1

/

6

100%