Types et performances des processeurs

Eduardo Sanchez

Laboratoire de Systèmes Logiques

Ecole Polytechnique Fédérale de Lausanne

Types et performances

des processeurs

Eduardo Sanchez

Ecole Polytechnique Fédérale de Lausanne

Page 2

Structure d’un ordinateur

processeur

mémoire entrées/sorties

bus d’adresse

bus de données

bus de contrôle

séquenceur

séquenceur

micromémoire

micromémoire

registres

registres

opérateurs

opérateurs

contrôle traitement

Eduardo Sanchez

Ecole Polytechnique Fédérale de Lausanne

Page 3

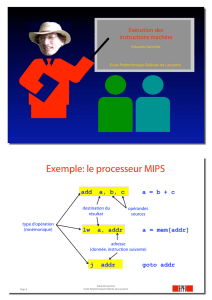

♦Un processeur effectue sans arrêt une boucle composée de trois

phases:

•recherche (fetch) de l’instruction: l’adresse en mémoire de l’instruction à

exécuter est stockée en permanence dans un registre du processeur, appelé

PC (Program Counter). L’instruction pointée par le PC est cherchée dans la

mémoire et stockée dans un autre registre du processeur: le IR (Instruction

Register)

•décodage de l’instruction (decode): chaque instruction est identifiée, grâce à

un code (opcode). En fonction de ce code, le processeur choisit la tâche à

exécuter, c’est-à-dire la séquence de micro-instructions à exécuter

•exécution (execute) de l’instruction: à la fin de cette phase, on retourne à la

première phase

Exécution d’une instruction

Eduardo Sanchez

Ecole Polytechnique Fédérale de Lausanne

Page 4

lecture de l’instruction

lecture de l’instruction

décodage

décodage

ADD

ADD MOVE

MOVE LOAD

LOAD STORE

STORE

initialisation

initialisation

•••••

Eduardo Sanchez

Ecole Polytechnique Fédérale de Lausanne

Page 5

MAR ←PC

MDR ←M[PC]

PC ←PC+1

IR ←MDR

MAR ←PC

MDR ←M[PC]

PC ←PC+1

IR ←MDR

chercher l’opérande

chercher l’opérande

exécuter

exécuter

PC←adresse initiale

PC←adresse initiale

décodification de IR

décodification de IR

opérande

opérande

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

1

/

29

100%