View PDF - CiteSeerX

ISSN 0249-6399

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

apport

de recherche

1993

PROGRAMME 1

Architectures parallèles,

bases de données,

réseaux et systèmes distribués

Briques de base pour la r´

ealisation

d’architectures parall`

eles sp´

ecialis´

ees

Fran¸cois Charot

N˚ 1977

Avril 1993

Briques de base pour la r´

ealisation d’architectures

parall`

eles sp´

ecialis´

ees

Fran¸cois Charot

Programme 1 — Architectures parall`

eles, bases de donn´

ees, r´

eseaux

et syst`

emes distribu´

es

Projet API

Rapport de recherche n˚1977 — Avril 1993 — 23 pages

R´

esum´

e : Les ´

etudes et recherches li´

ees au d´

eveloppement d’applications de

traitement d’image et plus particuli`

erement en traitement num´

erique du signal

vid´

eo requi`

erent des composants flexibles permettant la mise en œuvre “en vraie

grandeur” des algorithmes en vue de leur validation dans un contexte temps r´

eel.

L’objectif de ce rapport est de pr´

esenter les nouveaux circuits sp´

ecifiques

programmables “briques de base” pour la r´

ealisation d’architectures parall`

eles

sp´

ecialis´

ees. Lesapproches detypetraitement designal (DSP)deTexasInstruments

et Motorola, celles orient´

ees traitement d’image et du signal propos´

ees par Intel

(iWARP), ainsi que les circuits de traitement vid´

eo de Philips, NEC et ITT sont

consid´

er´

es.

Mots-cl´

e : processeur sp´

ecialis´

e programmable , DSP, VSP

(Abstract: pto)

Unit´

e de recherche INRIA Rennes

IRISA, Campus universitaire de Beaulieu, 35042 RENNES Cedex (France)

T´

el´

ephone : (33) 99 84 71 00 – T´

el´

ecopie : (33) 99 38 38 32

Building blocks for the design of specialized parallel

architectures

Abstract: The study and research in the area of image processing and espe-

cially in video signal processing require flexible components that allow real-time

implementation of the algorithms to be considered.

In the report, we present the new specialized programmable circuits, building

blocks for the implementation of specialized parallel architectures. The dsp-based

approaches fromTexas Instrumentsand Motorola, those suited to image and signal

processingproposedbyIntel(iWARP),andalsothevideosignalprocesssingcircuits

from Philips, NEC and ITT are described.

Key-words: Specialized programmable processor, DSP, VSP

Briques de base pour la r´ealisation d’architectures parall`eles sp´ecialis´ees 1

Introduction

Les applications de traitement d’image et plus particuli`

erement les applications de

traitement vid´

eo impliquent des algorithmes de plus en plus complexes. Il ne s’agit

plus uniquement de mettre en œuvre un traitement ou un algorithme de base mais

de maˆ

ıtriser toute une application faite d’un certain nombre de traitements de base

qui interagissent. La mise au point, l’´

emulation et l’´

evaluation de ces applications

complexes n´

ecessitent des architectures parall`

eles sp´

ecialis´

ees qui doivent ˆ

etre:

programmables et polyvalentes pour pouvoir effectuer les algorithmes sou-

haite´s et s’adapter aux e´volutions pre´visibles dans le domaine des algo-

rithmes;

modulaires. La modularit´

e est une garantie sur les possibilit´

es d’´

evolution

de la machine et permet une adaptation ais´

ee `

a des contextes applicatifs

diff´

erents (adaptation `

a la complexit´

e du type de probl`

eme `

a traiter).

Les ´

etudes et recherches li´

ees au de´veloppement de telles applications com-

plexes ont justifie´ le de´veloppement de composants flexibles permettant la mise

en œuvre “en vraie grandeur” des algorithmes en vue de leur validation dans un

contexte temps r´

eel. Parmi les nouveaux circuits spe´cifiques programmablesappa-

rus sur le marche´, les re´alisations les plus caracte´ristiques incluent les approches

traitement de signal (DSP) propose´es par Texas Instruments ou Motorola, celles

oriente´es traitement d’image ou de signal ou traitement nume´rique (processeur

iWARP d’Intel), enfin, des composants appele´s processeurs de traitement de signal

vide´o (VSP) sont maintenant e´tudie´s et propose´es par quelques industriels (Philips,

NEC et ITT).

Ces nouveaux processeurs, dont l’architecture est d´

etaill´

ee dans ce rapport, ont

en commun les caract´

eristiques suivantes.

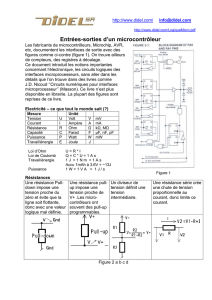

Leurs possibilite´s d’entre´e/sortie permettent la re´alisation efficace de struc-

tures paralle`les (briques de base) et la mise en œuvre de communications

interprocesseurs `

a haut de´bit, et ce, sans ajout de logique externe.

Leurs capacit´

es de calcul (en arithm´

etique en virgule flottante pour certains)

sont consid´

erables.

L’organisation de leurs architectures internes est telle que plusieurs ope´ra-

tions peuvent ˆ

etre lance´es en paralle`le.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

1

/

28

100%