Architecture et Syst`eme

Architecture et Syst`

eme

Stefan Schwoon

Cours L3, 2016/17, ENS Cachan

Multiplexeur

Supposons qu’on poss`

ede kvaleurs en entr ´

ee (ou k= 2n), pour n≥1), ou

chacune des valeurs x0,...,xk−1est un mot de mbits.

On souhaite s´

electionner l’une de ces valeurs par son indice, p.ex. ´

etant donn´

es

(cod´

e par nbits), on souhaite renvoyer xs.

Applications:

Lire un mot dans la m´

emoire en sp´

ecifiant son adresse.

Choisir entre plusieurs sources de donn´

ees.

Obtenir une valeur dans un tableau pr´

e-calcul´

e.

2

Multiplexeur : Exemple

Supposons m=n= 1, du coup on poss`

ede deux bits x0,x1et un bit de

s´

election s0.

Solution: on r´

ealise la fonction (x0∧ ¬s0)∨(x1∧s0).

Supposons m= 1,n= 2, du coup on poss´

ede x0,··· ,x3et s1s0:

Dans un premier temps, on ´

evalue s0pour s ´

electionner (en parall`

ele) entre

x0,x1et x2,x3.

Dans un deuxi`

eme temps, on ´

evalue s1pour s ´

electionner parmi les deux bits

choisis avant.

Le probl`

eme se g´

eneralise pour n>2avec un circuit de profondeur O(n).

Pour m>1: On utilise mcircuits en parall`

ele, un par bit.

3

D´

ecodeur

On poss`

ede une valeur scod ´

ee par nbits et 2nsorties y0,...,y2n−1.

Sortie : ys= 1 et ys0= 0 pour tout s06=s.

Solution (facile) : Pour tout 0≤s0<2n, on construit la conjonction qui ´

evalue si

s0=s.

Applications :

S´

electionner une cellule sp´

ecifique dans la m´

emoire.

S´

electionner un p´

eriph´

erique parmi plusieurs pour ´

echanger des donn´

ees.

4

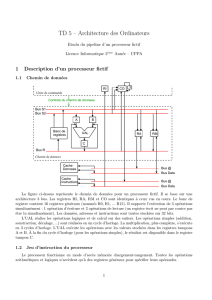

Symboles

Les symboles typiquement utilis´

es pour les multiplexeurs et d´

ecodeurs :

m

m m

x0x2n−1

sn

y

n

...

s

y0y2n−1

decode

...

MUX

Les barres diagonales indiquent que le fil transf`

ere un mot de la taille indiqu´

ee `

a

cˆ

ot´

e (c’est `

a dire il s’agit d’une collection d’autant de bits).

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

1

/

27

100%