0903ProcCheminDonneesVHDL

INF3500 : Conception et implémentation de systèmes numériques

http://creativecommons.org/licenses/by-nc-sa/2.5/ca/

Pierre Langlois

Modélisation VHDL du chemin des données

d’un processeur à usage général

INF3500 : Conception et implémentation de systèmes numériques

Modélisation VHDL du chemin des données d’un processeur à usage général

Sujets de ce thème

•Rappel: architecture du processeur PolyRISC et son chemin des données

•Modélisation du bloc des registres

•Modélisation de l’unité arithmétique et logique

•Modélisation de la mémoire des données

•Implémenter la mémoire des données dans un FPGA

2

INF3500 : Conception et implémentation de systèmes numériques

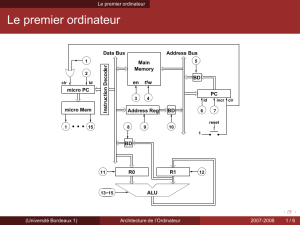

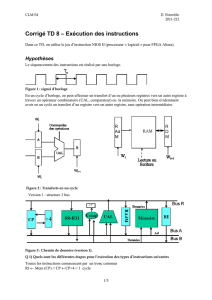

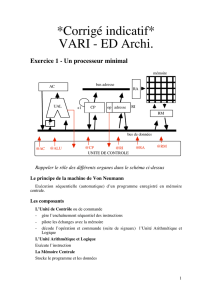

Le processeur à usage général PolyRISC

3

CP

UAL

B

A

F

Z

N

op_UAL

B

choixCharge

Bloc des registres

chargeBR

choixB

choixA

AdonnéeBR

UBbrancher

condition

Z

N

Mémoire des données

donnee_MD

adresse

charge_MD

M[adresse]

Mémoire des

instructions

choixB_UAL

choixDonnee_BR

`

valeur

UAL: Unité arithmétique et logique

UB: Unité de branchement

CP: Compteur de programme

Op_UAL:

0: F <= A

1: F <= B

2: F <= A + B

3: F <= A – B

4: F <= A ET B

5: F <= A OU B

6: F <= NON A

7: F <= A OUX B

adresse instruction

1

Décodage

INF3500 : Conception et implémentation de systèmes numériques

UAL

B

A

F

Z

N

op_UAL

B

choixCharge

Bloc des registres

chargeBR

choixB

choixA

AdonnéeBR

Mémoire des données

donnee_MD

adresse

charge_MD

M[adresse]

choixB_UAL

choixDonnee_BR

`

valeur

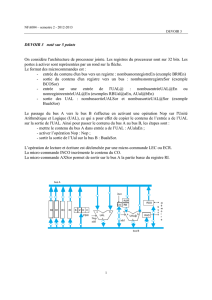

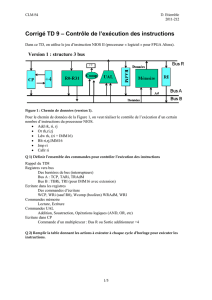

Chemin des données du processeur PolyRISC

•Nous allons voir comment modéliser les trois

composantes du chemin des données:

1. Le bloc des registres

2. L’unité arithmétique et logique

3. La mémoire des données

4

INF3500 : Conception et implémentation de systèmes numériques

1. Bloc de registres

•Un bloc de registre contient:

–Des registres

–Un mécanisme pour les charger à partir

d’un port d’entrée

–Un mécanisme pour aiguiller leur valeur

à des ports de sortie

•Un bloc de registre peut avoir plusieurs

ports d’entrée et de sortie.

•Un registre peut être simultanément la

cible d’une écriture et la source pour

l’un des ports de sortie.

5

R0

D Q

charge

R1

D Q

charge

R2

D Q

charge

R3

D Q

charge

choixA

choixB

0

1

2

3

chargeBR

choixCharge

donnéeBR

A

B

2:4

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

1

/

13

100%