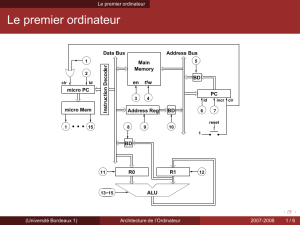

Unité de Traitement (CPU) : UAL et UCC

1

CHAPITRE 3

L’UNITE DE TRAITEMENT ( CPU)

Introduction :

L’unité centrale de traitement (UCT) appelée aussi processeur central (Central Processing

Unit = CPU) est l’élément moteur de l’ordinateur qui interprète et exécute les instructions

du programme. Il est intimement associé à la mémoire centrale ou sont stockées ces

instructions avec leurs données à traiter elle est composée de deux unités fonctionnelles.

L’unité arithmétique et logique (UAL) qui effectue les opérations arithmétiques et

logiques.

L’unité de contrôle et de commande (UCC) qui commande l’exécution de toutes les

opérations à tous les niveaux (UAL, MC, E/S) ainsi que le contrôle de leur

déroulement.

Comment fonctionne l’ensemble UCC et UAL ?

On suppose un programme en cours d’exécution, les instructions et les données sont stockées

en mémoire centrale à des adresses bien définies, comment se déroule l’exécution d’une

instruction ?

L’unité de contrôle et commande cherche en mémoire centrale l’instruction en lui

envoyant une adresse et une commande.

L’instruction est transférée vers l’UCC pour décodage, qui va déterminer l’opération à

exécuter.

Des signaux sont envoyés à l’UALpour déclencher l’opération.

Les données nécessaires sont acheminées de la mémoire centrale MC vers l’unité

arithmétique et logique (UAL).

Une fois l’exécution terminée, les résultats sont envoyés à la mémoire centrale.

Exemple :

On considère le programme PASCAL suivant :

Begin Read(a) ;

Read(b) ;

S :=a+b ;

Write(S)

End.

2

Une fois le programme lancé, l’unité de traitement commande d’introduire les données en

mémoire qui seront introduites par clavier et occupent des emplacements en mémoire

centrale.

l’exécution de l’instruction S :=a+b engendre les opérations suivantes :

Transfert de l’instruction vers l’UCC ou elle est décodée.

Transfert des deux opérandes vers l’UAL .

Exécution de l’opération d’addition.

Transfert du résultat vers la mémoire

L’instruction Write(S) engendre :

Une commande de lecture du contenu de la variable S en mémoire centrale

Une commande d’entrée/sortie adressée au périphérique concerné (écran)

Transfert du contenu de la variable S pour son affichage sur écran.

Begin et End annoncent le début et la fin du programme.

1-L’unité arithmétique et logique UAL

Elle effectue des opérations arithmétiques et logiques, elle est dotée de circuits logiques

capables de réaliser les fonctions logiques ET, OU, NON, etc, et des opérations

arithmétiques addition, soustraction, division, décalage, test d’infériorité, supériorité…etc.

Réalisation d’une UAL 1 bit

Pour concevoir une UAL à 1 bit qui traite 4 opérations a ET b, a OU b, NON b, a+b

On doit disposer d’un circuit capable de sélectionner l’opération à exécuter, ce circuit doit

avoir deux entrées F0 et F1, à partir desquelles, on peut effectuer 4 choix (00, 01, 10, 11)

ce circuit ne peut être qu’un décodeur à deux bits.

Pour réaliser l’opération arithmétique A+B, on utilise un circuit appelé additionneur, il doit

prendre en considération une éventuelle retenue.

F0 F1 Décodeur

3

Cette UAL est capable de calculer le ET, le OU de 2 bits, le NON du second bit, et la somme

des 2 bits avec une retenue d’entrée. Le choix parmi ces quatre opérations se fait via les deux

lignes de commandes F0 et F1. Suivant la valeur de ces 2 bits, le décodeur active une des

quatre lignes de sortie, sélectionnant soit une des trois fonctions logiques (aet b,aou b,

non b) soit la retenue et la sortie de l’additionneur. Ainsi en reliant chacune des trois

premières sorties du décodeur à la porte logique appropriée par une porte AND on active

une des 3 opérations logiques et en reliant la quatrième sortie à l’additionneur par une porte

AND on active l’additionneur et notre schéma complet de l’UAL 1 bit sera le suivant :

retenue

Remarque : pour réaliser une UAL à n bits on a qu’à relier n circuits d’UAL à 1 bits.

Une UAL peut être caractérisée par sa taille et ses possibilités Sa taille, ou largeur, correspond

a la taille maximale des nombres que l’UAL peut traiter Les possibilités de l’UAL

correspondent simplement aux différentes commandes qu’elle reconnaît.

Le constructeur d’un processeur a toujours la possibilité d’étendre les capacités de l’UAL (en

autorisant des opérations plus complexes) ou d’augmenter sa taille (pour permettre la

manipulation de nombres plus grands). Mais cela implique d’utiliser plus de portes logiques et

donc d’occuper plus de place sur la puce, au détriment des autres circuits.

4

2-L’unité de commande et de contrôle UCC :

L’UCC accomplit deux fonctions : commander et contrôler en utilisant des circuits pour

décoder les instructions du programme et les transformer en signaux de commande vers toutes

ces unîtes.

2-1- structure d’une UCC

Les principaux éléments d’une UCC qui lui permettent d’accomplir ces taches sont.

a-Le compteur ordinal (CO)

Le registre CO (Program Counter = PC) contient toujours l’adresse en mémoire de la

prochaine instruction à exécuter. Le CO est automatiquement incrémenté après exécution de

chaque instruction, ainsi le programme est exécuté en séquence à moins qu’il contienne une

instruction modifiant la séquence (par exemple, une instruction de saut ou un branchement).

Dans ce cas, la nouvelle adresse remplacera le contenu du CO.

b- Le registre instruction (RI)

Lorsque le processeur va chercher une instruction en cours d’exécution en mémoire, il la

place dans le RI. La taille du RI correspond à la taille du mot mémoire . Le programmeur n’a

pas accès au RI. Les bits correspondants à la zone « code opération », sont envoyés au

décodeur pour qu’il détermine l’opération à exécuter.

c- Le décodeur :

C’est un circuit combinatoire qui détermine quelle opération doit être effectuée

(étudié en chapitre 2).

d-Le séquenceur :

Le séquenceur est un automate qui génère les signaux de commande nécessaires pour

actionner et contrôler les unités qui participent à l’exécution d’une instruction donnée il peut

être réalisé de 2 façons.

Câblé : circuit séquentiel complexe qui fait correspondre à chaque instruction exécutable un

sous-circuit capable de commander son déroulement. Le sous-circuit approprié est activé par

un signal provenant du décodeur

Microprogrammé : suite de micro-instructions stockées dans une mémoire rapide.

.Ce microprogramme génère une suite de signaux de commandes équivalents à celle produites

par un séquenceur câblé.

e- L’horloge :

Le rôle de l’horloge dans l’UCC est de générer des signaux périodiques qui définissent le

cycle machine qui correspond à la durée élémentaire régissant le fonctionnement de la

machine, il synchronise toutes les actions du processeur.

2-2 Fonctionnement d’une UCC :

Essayons de suivre les étapes d’exécution d’une instruction machine cette instruction

comporte 2 champs.

Code opération (obligatoire).

un ou plusieurs champs adresse.

Instruction = code opération + adresse opérande

L’instruction passe par 2 cycles.

-Cycle de recherche : cherche l’instruction et décode.

-Cycle d’exécution :exécution par l’UAL de l’instruction.

5

On résume le cycle de recherche par :

1. Transfert de l’adresse de la nouvelle instruction à exécuter du CO vers le registre

adresse mémoire RA (en MC)

2. Une commande est généré par l’UCC pour lire l’instruction et l’envoyer vers le

registre RM.

3. L’instruction est transférée dans RI (code op + adresse op).

4. Pendant que l’adresse de l’opérande est envoyée vers RA le code opération est

transmis au décodeur qui détermine le type de l’opération et le transmet au

séquenceur.

5. Le CO est incrémenté pour le suivant le cycle de recherche s’il ne s’agit pas d’une

instruction de branchement.

Le cycle d’exécution comprend les étapes suivantes :

1- Le séquencer lance des signaux de commande vers le mémoire pour lire l’opérande à

l’adresse déjà stockée dans le RA et le transférer dans RM.

2- Transfert du contenu de RM vers l’UAL, et plus précisément vers l’accumulateur ou

tout autre registre affecté à l’opération spécifiée.

3- L’opération est effectuée sous contrôle du séquenceur.

4- L’opération est effectuée sous cont

Cycle d’exécution d’une instruction

Cycle de recherche d’une instruction

6

6

7

7

8

8

9

9

10

10

1

/

10

100%