LE BUS PCI

1

LES BUS NUMERIQUES

Bus parallèles

Le bus PCI

Cours_bus_PCI_0_02

2

LE BUS PCI

Sommaire

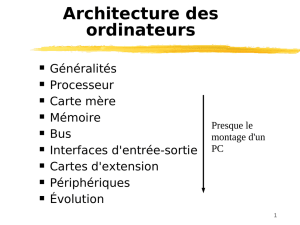

Première partie: Présentation

Deuxième partie: Les signaux

Troisième partie: Les échanges de données

Quatrième partie: L’Arbitrage

Cinquième partie: Les transactions particulières

Sixième partie: Les aspects électriques, timings

Septième partie: Bridge PCI / PCI

Huitième partie: L’espace de configuration

Neuvième partie: Les performances

3

LE BUS PCI

1ière partie: Présentation

Sommaire - Repère

Première partie: Présentation

Glossaire

Historique

L’évolution vers le PCI

•Le couplage direct

•Connexion directe bufferisée

•Connexion par bus local indépendant

Le bus ISA

Le bus EISA

Le VL Bus

La création du standard PCI et ses évolutions

Le bus PCI: Concept et intérêts

Aspects techniques

Aspects économiques

Les principales caractéristiques

1ière partie: Présentation

2ième partie: Les signaux

3ième partie: Les échanges de données

4ième partie: L ’Arbitrage

5ième partie: Les transactions particulières

6ième partie: Les aspects électriques, timings

7ième partie: Bridge PCI / PCI

8ième partie: L ’espace de configuration

9ième partie: Les performances

4

LE BUS PCI

1ière partie: Présentation

Glossaire

Agent Élément matériel relié au bus PCI.

Arbitre Élément matériel chargé de gérer les demandes d ’accès

au bus des différents initiateurs.

Physiquement, l ’arbitre peut être n ’importe où.

Cible Aussi appelé Esclave ou Target

Élément matériel uniquement capable de recevoir ou

d’émettre des données sur demande d ’un Initiateur

Contrôleur d ’interruptions Logique chargée de reconnaître des interruptions et de

gérer les échanges nécessaires

Idle State État inoccupé du bus PCI

Initiateur Aussi appelé Maître

Élément matériel susceptible de prendre le bus pour gérer

un échange

IRQ Interrupt request

Turn-around cycle Cycle mort noté sur les chronogrammes et nécessaire

pour permettre d ’éviter des contentions sur certains

signaux pouvant être drivés par plusieurs agents PCI

5

LE BUS PCI

1ière partie: Présentation

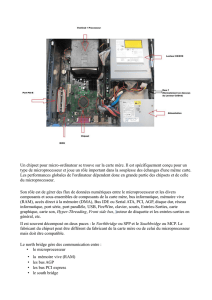

Historique: L ’évolution vers le PCI; Le couplage direct

Avantages:

Facilité de mise en œuvre

Faible coût

Inconvénients

Structure dépendante du processeur

Peu de périphériques rapides

Augmentation du taux d ’occupation du

bus processeur

Bus processeur 32 bits à 33 MHz

Contrôleur de bus

d'extension ISA

Cache

Mémoire Centrale

Bus de données 16 bits à 8,33 MHz

SCSI Vidéo Réseau

local Lecteur

disquettes Modem

Processeur

Périphérique

rapide

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

1

/

17

100%