ppt, 199KB

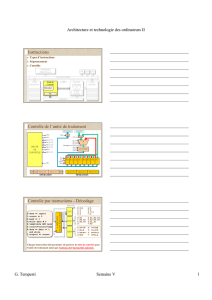

Instructions

Types d’instructions

Séquencement

Contrôle

BUS SYSTÈME

Registres

Unité de

Traitement

Unité

Flottante

Unité de

Contrôle

Décodeur

PC

ALU

CPU

MÉMOIRE

PRINCIPALE IO IO IO

Cache

Données

Cache

Instructions

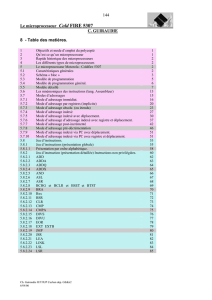

Contrôle de l’unité de traitement

UNITÉ

DE

CONTRÔLE

OEN

SEL

AL[2:0]

SH[2:0]

RA[2:0]

RB[2:0]

WEN

WA[2:0]

3

3

3

3

3

Z≠0

OEN SEL AL[2:0] SH[2:0] RA[2:0] RB[2:0]WEN WA[2:0]

OPÉRATION OPÉRANDES

RA

WA

RB

WEN

I0I1

Z

SHIFTER

R0 R1 R2 R3 R4 R5 R6 R7

SH2

SH1

SH0

AL2

AL1

AL0

OEN

SEL

Z≠0

1 0

INPORTOUTPORT

3

3

3

Contrôle par instructions - Décodage

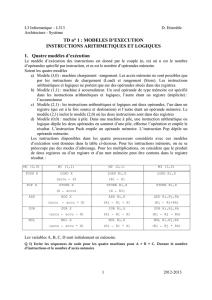

0:R1 4:R1,R3,R4

1:R0,R2 5:R2,R4,R2

2:R0,R3 6:R1,R1

3: 7:R2

0:AIN 4: CA&B

1:BA 5: CA+B

2:BA+1 6: BA>>1

3:NOP 7: OUTA

0:0|1 4:5

1:2 5:6

2:3 6:7|4

3:4 7:0

0:data inport

1:ocount 0

2:mask 1

3:while data ≠ 0

4:tempdata AND mask

5:ocountocount+temp

6:data data >> 1

end while

7:outport ocount

SLC

CK

n BASCULES

Opcode Opérandes

Fanions

RAM

Contrôle

SLC

Opérandes

Instruction

Adresse

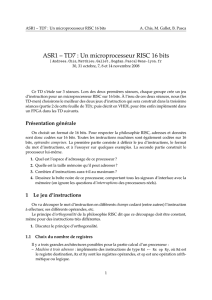

Chaque instruction doit permettre de générer les bits de contrôle pour

l’unité de traitement ainsi que l’adresse de l’instruction suivante.

Format des instructions: exemple

Le codage des instructions est, en général, arbitraire:

OPCODE OPER1 OPER2 OPER3

LOAD ADR, R1 0 0 0 Adresse[5:0] 0 0 1

MOVE R0, R2 0 0 1 0 0 0 0 1 0 ø ø ø

INC R0, R3 0 1 0 0 0 0 0 1 1 ø ø ø

BRA ADR, COND 0 1 1 Adresse[5:0] data=0

AND R1, R3, R4 1 0 0 0 0 1 0 1 1 1 0 0

ADD R2, R4, R2 1 0 1 0 1 0 1 0 0 0 1 0

SHR R1, R1 1 1 0 0 0 1 0 0 1 ø ø ø

BRA ADR, COND 0 1 1 Adresse[5:0] vrai

STORE ADR, R2 1 1 1 Adresse[5:0] 0 1 0

Compilation

program toto;

var

A, B, C : array [1...1000] of integer;

i : integer

begin

...

for i:=1 to 1000 do

C[i] := A[i] + B[i];

...

end

Algorithme

Langage de haut-niveau

Langage machine

= jeu d’instructions

COMPILATEUR

...

MOVE.L #2001,A0

MOVE.L #3001,A1

MOVE.L #4001,A2

START: ABCD -(A0),-(A1)

MOVE.B (A1),(A2)

TEST: CMPA #1001, A0

BNE START

...

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

1

/

30

100%