Langage d`assemblage

Langage d’assemblage :

I. Définition

Langage qui permet de définir en détail chaque instruction d’un programme. L’assembleur,

programme qui va traduire un programme en langage d’assemblage en programme en code machine

(binaire)

II. Langage d’assemblage μPIUP

Une ligne par instruction

o Label (étiquette) : symbole en début de ligne qui représente une adresse

o Mnémonique d’opération : indique l’opération effectuée par un mot assez court (ex :

ADD, ADC, LDW, …)

o Opérandes : de 0 à 3 opérandes selon les instructions. Séparées par des virgules,

certains sont sources, d’autres destinataires. Pour chaque opérande, on définit un

mode d’adressage, un registre et/ou une constante.

Label (étiquette)

Mnémonique

d’opération

Opérande(s)

// Commentaires

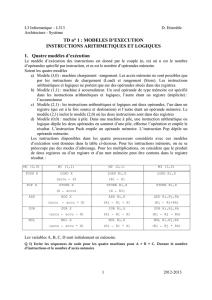

III. Modes d’adressage. Ecriture des opérandes.

Mode

Syntaxe

Exemple

Valeur opérande

Adresse opérande

Registre

Ri

R3

Contenu R3

-

Basé,

indirect

(Ri)

R3

Contenu de la case mémoire dont

l’adresse est dans R3 (pointé par R3)

Immédiat

#Constante

#3

3 qui est dans le mot d’extension de

l’instruction (qui suit le code

d’instruction)

Contenu du PC, car il

pointe sur le mot qui

suit le code

d’instruction

#0xF30A

(F30A)16 hexadécimal

Direct

@ adresse

@0xF30A

Contenu de la case mémoire dont

l’adresse est indiquée

0xF30A = contenu du

mot d’extension

IV. Exemples d’instructions.

ADD R2, R3, R1 //Charge R1 avec la somme de R2 et R3

NEG R4, R3 // charge R3 avec le complément à 2 (l’opposé) du contenu de R4

STC // met l’indicateur CF à 1 (SeT Carry)

(mode direct) LDW R1, @0xFF04 // charge R1 avec le mot mémoire d’adresse FF04

(mode registre) LDW R1, R2 // charge R1 sur le contenu de R2

(mode immédiat) LDW R1, #3 // charge R1 avec la valeur constante 3

(mode basé) LDW R1, (R2) // charge R1 avec le contenu de la case mémoire

pointée par R2

Code

Type

01

Byte

10

Word

11

Long word

LDB R1, @0xFF03 // charge l’octet d’adresse FF03 dans R1

LDB R1, (R2) // charge l’octet pointé par R2 dans R1

Attention : ces instructions sont impossibles :

LDW R1, @OxFF03 // l’adresse est impaire or les mots sont à des adresses paires

LDB R1, R2 // les instructions en mode registre ne gèrent que des mots

ADD R1, (R2), R3 // ADD ne gère que le mode registre

Groupe rapide :

« Mode rapide ». La constante est codée en code complément à 2 dans l’octet droit du code

d’instruction.

LDQ 3, R2 // charge R2 avec 3

ADQ 3, R2 // ajoute 3 au registre de R2

Instructions de branchement relatif, court (et rapide) :

BEQ 52 // branche à l’instruction cible dont l’adresse est PC # 52 (soit l’adresse

de l’instruction courante + 2 + 52)

L’opérande est l’instruction cible.

Intérêt du mode d’adressage relatif : translatable et réglable

Branchement relatif, long (et lent) :

JEQ #52 // branche à l’instruction cible dont l’adresse est PC # 52.

L’adresse de l’instruction cible est relative au PC et le déplacement est en mode immédiat.

Branchement absolu :

JEA @0xFF00 // branche sans condition à l’instruction cible dont l’adresse est FF00

(Jump to Effective Address)

L’opérande est l’instruction cible.

1

/

2

100%