Architecture et technologie des ordinateurs II G. Tempesti Semaine

Architecture et technologie des ordinateurs II

G. Tempesti Semaine V 1

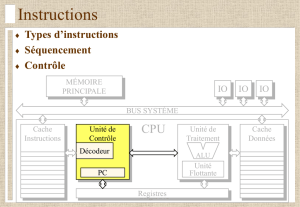

Instructions

®Types d’instructions

®Séquencement

®Contrôle

BUS SYSTÈME

Registres

Registres

Unité de

Traitement

Unité de

Traitement

Unité

Flottante

Unité de

Contrôle

Unité de

Contrôle

Décodeur

PC

ALU

CPU

MÉMOIRE

PRINCIPALE

MÉMOIRE

PRINCIPALE IO

IO IO

IO IO

IO

Cache

Données

Cache

Instructions

Contrôle de l’unité de traitement

UNITÉ

DE

CONTRÔLE

OEN

SEL

AL[2:0]

SH[2:0]

RA[2:0]

RB[2:0]

WEN

WA[2:0]

3

3

3

3

3

Zπ0

OEN

OEN SEL

SEL AL[2:0]

AL[2:0] SH[2:0]

SH[2:0] RA[2:0]

RA[2:0] RB[2:0]

RB[2:0]

WEN

WEN WA[2:0]

WA[2:0]

OPÉRATION OPÉRANDES

RA

WA

RB

WEN

I0I1

Z

SHIFTER

R0 R1 R2 R3 R4 R5 R6 R7

SH2

SH1

SH0

AL2

AL1

AL0

OEN SEL

Zπ0

1 0

INPORTOUTPORT

3

3

3

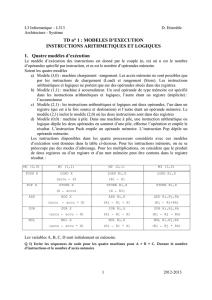

Contrôle par instructions - Décodage

0:R1 4:R1,R3,R4

1:R0,R2 5:R2,R4,R2

2:R0,R3 6:R1,R1

3: 7:R2

0:A¨¨

¨¨IN 4: C¨¨

¨¨A&B

1:B¨¨

¨¨A 5: C¨¨

¨¨A+B

2:B¨¨

¨¨A+1 6: B¨¨

¨¨A>>1

3:NOP 7: OUT¨¨

¨¨A

0:0|1 4:5

1:2 5:6

2:3 6:7|4

3:4 7:0

0:data ¨¨

¨¨ inport

1:ocount ¨¨

¨¨ 0

2:mask ¨¨

¨¨ 1

3:while data ππ

ππ 0

4:temp¨¨

¨¨data AND mask

5:ocount¨¨

¨¨ocount+temp

6:data ¨¨

¨¨ data >> 1

end while

7:outport ¨¨

¨¨ ocount

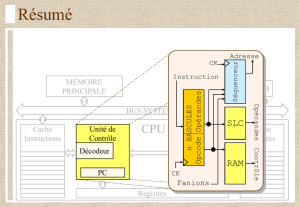

SLC

SLC

CK

n BASCULES

Opcode Opérandes

n BASCULES

Opcode Opérandes

Fanions

RAM

RAM

Contrôle

SLC

SLC

Opérandes

Instruction

Adresse

Chaque instruction doit permettre de générer les bits de contrôle pour

l’unité de traitement ainsi que l’adresse de l’instruction suivante.

Architecture et technologie des ordinateurs II

G. Tempesti Semaine V 2

Format des instructions: exemple

Le codage des instructions est, en général, arbitraire:

OPCODE OPER1 OPER2 OPER3

LOAD ADR, R1 0 0 0 Adresse[5:0] 0 0 1

MOVE R0, R2 0 0 1 0 0 0 0 1 0 ø ø ø

INC R0, R3 0 1 0 0 0 0 0 1 1 ø ø ø

BRA ADR, COND 0 1 1 Adresse[5:0] data=0

AND R1, R3, R4 1 0 0 0 0 1 0 1 1 1 0 0

ADD R2, R4, R2 1 0 1 0 1 0 1 0 0 0 1 0

SHR R1, R1 1 1 0 0 0 1 0 0 1 ø ø ø

BRA ADR, COND 0 1 1 Adresse[5:0] vrai

STORE ADR, R2 1 1 1 Adresse[5:0] 0 1 0

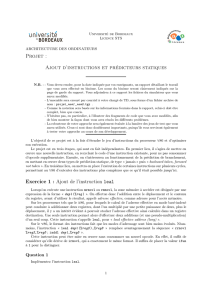

Compilation

program toto;

var

A, B, C : array [1...1000] of integer;

i : integer

begin

...

for i:=1 to 1000 do

C[i] := A[i] + B[i];

...

end

program toto;

var

A, B, C : array [1...1000] of integer;

i : integer

begin

...

for i:=1 to 1000 do

C[i] := A[i] + B[i];

...

end

Algorithme

flfl

flfl

Langage de haut-niveau

flfl

flfl

Langage machine

= jeu d’instructions

Algorithme

flfl

flfl

Langage de haut-niveau

flfl

flfl

Langage machine

= jeu d’instructions

COMPILATEUR

COMPILATEUR

...

MOVE.L #2001,A0

MOVE.L #3001,A1

MOVE.L #4001,A2

START: ABCD -(A0),-(A1)

MOVE.B (A1),(A2)

TEST: CMPA #1001, A0

BNE START

...

...

MOVE.L #2001,A0

MOVE.L #3001,A1

MOVE.L #4001,A2

START: ABCD -(A0),-(A1)

MOVE.B (A1),(A2)

TEST: CMPA #1001, A0

BNE START

...

Opération du processeur - Opcodes

Un processeur non-spécialisé (general-purpose) doit avoir un

jeu d’instructions qui soit:

¾Complet: il doit pouvoir exécuter toute fonction calculable;

¾Efficace: il doit exécuter rapidement les fonctions les plus utilisées;

¾Régulier: il doit contenir les fonctions attendues (p.ex., s’il y a un

décalage à gauche, il doit y avoir un décalage à droite);

¾Compatible?: si nécessaire, il doit être compatible avec le jeu d’une

machine existante.

Tout algorithme est réalisé par une séquence (série)

d’instructions.

Architecture et technologie des ordinateurs II

G. Tempesti Semaine V 3

Boucle de traitement

Début

Début

Instructions

en attente?

Instructions

en attente?

Chargement

Chargement

Décodage

Décodage

Interruptions

en attente?

Interruptions

en attente?

Traitement

Traitement

OUI

NON

NON

OUI

Les instructions sont stockées en mémoire,

comme n’importe quelle donnée. À chaque

instruction correspond donc un adresse.

Chaque instruction est chargée dans le

processeur, décodée pour déterminer sa

fonction et les bits de contrôle pour l’unité de

traitement sont générés en conséquence.

L’unité de traitement effectue l’opération

désirée sur les données.

Si une interruption est en attente, elle a

normalement précédence sur les instructions,

et elle est donc traitée immédiatement.

Types d’instructions - Opcode

¾Transfert de données

Transferts d’informations entre positions mémoire (interne ou

externe au processeur)

¾Arithmétique

Opérations sur données numériques

¾Logique

Opérations booléennes et autres

¾Entrées/sorties (I/O)

Transferts d’informations entre le processeur ou la RAM et les

unités externes

¾Contrôle

Instructions qui modifient le flot d’instructions

Format des instructions: exemple

data ¨¨

¨¨ inport = LOAD ADR, R1 [T]

ocount ¨¨

¨¨ 0= MOVE R0, R2 [T]

mask ¨¨

¨¨ 1 = INC R0, R3 [A]

while data ππ

ππ 0 = BRA COND, ADR [C]

temp ¨¨

¨¨ data AND mask = AND R1, R3, R4 [L]

ocount ¨¨

¨¨ ocount + temp = ADD R2, R4, R2 [A]

data ¨¨

¨¨ data >> 1 = SHR R1, R1 [L]

end while = BRA 1, ADR [C]

outport ¨¨

¨¨ ocount = STORE ADR, R2 [T]

Architecture et technologie des ordinateurs II

G. Tempesti Semaine V 4

Format des instructions

Beaucoup d’information! P.ex., une architecture avec 256 instructions,

16 fanions, 64 registres et un bus (adresse) de 32 bits aurait besoin,

même si tous les opérandes sont des registres (ce qui n’est pas le cas),

de 8 + 4 + 6x3 + 32x2 = 94 bits!

Une solution est de coder les instructions sur plusieurs mots mémoire.

Ce fut une technique très utilisée dans le passé (processeurs 8 et 16

bits) et le reste aujourd’hui pour certains types d’instructions. Elle

introduit cependant beaucoup de délai (plusieurs coups d’horloge par

instruction, décodage complexe).

Des simplifications sont nécessaires!

Opcode

Opcode Conditions

Conditions Opérandes (3)

Opérandes (3) Prochaine(s) instruction(s)

Prochaine(s) instruction(s)

Format des instructions - Simplifications

Première simplification: chaque type d’instruction nécessite des

informations différentes.

Transferts de données: 78 bits (un opérande peut être une adresse)

Opérations arithmétiques et logiques: 58 bits (que des registres)

Opérations d’entrée/sortie: 78 bits (un opérande peut être une adresse)

Instructions de contrôle: 76 bits

Opcode

Opcode Opérandes (2)

Opérandes (2) Prochaine instruction

Prochaine instruction

Opcode

Opcode Opérandes (3)

Opérandes (3) Prochaine instruction

Prochaine instruction

Opcode

Opcode Opérandes (2)

Opérandes (2) Prochaine instruction

Prochaine instruction

Opcode

Opcode Conditions

Conditions Prochaine(s) instruction(s)

Prochaine(s) instruction(s)

SL

SL

CK

n BASCULES

Opcode Opérandes

n BASCULES

Opcode Opérandes

Fanions

RAM

RAM

Contrôle

SLC

SLC

Opérandes

Instruction

Adresse

Format des instructions - Simplifications

Deuxième simplification: par défaut, on peut définir la prochaine

instruction comme étant l’instruction suivante en mémoire.

0:+1|0 4:+1

1:+1 5:+1

2:+1 6:+1|4

3:+1 7:0

0:data ¨¨

¨¨ inport

1:ocount ¨¨

¨¨ 0

2:mask ¨¨

¨¨ 1

3:while data ππ

ππ 0

4:temp¨¨

¨¨data AND mask

5:ocount¨¨

¨¨ocount+temp

6:data ¨¨

¨¨ data >> 1

end while

7:outport ¨¨

¨¨ ocount

Architecture et technologie des ordinateurs II

G. Tempesti Semaine V 5

Séquenceur

Séquenceur

CK

n BASCULES

Opcode Opérandes

n BASCULES

Opcode Opérandes

Fanions

RAM

RAM

Contrôle

SLC

SLC

Opérandes

Instruction

Adresse

CK

Séquenceur

CK

Opérande

SLC

Opcode

Condition

Fanions

+1

Adresse

PC

Format des instructions - Simplifications

Transferts de données: 46 bits (un opérande peut être une adresse)

Opérations arithmétiques et logiques: 26 bits (que des registres)

Opérations d’entrée/sortie: 46 bits (un opérande peut être une adresse)

Instructions de contrôle: 44 bits

Toujours trop grandes! Il faut trouver d’autres simplifications.

Opcode

Opcode Opérandes (2)

Opérandes (2)

Opcode

Opcode Opérandes (3)

Opérandes (3)

Opcode

Opcode Opérandes (2)

Opérandes (2)

Opcode

Opcode Condition

Condition Prochaine instruction

Prochaine instruction

Les opérations arithmétiques et logiques peuvent, en théorie, être

effectuées directement sur des données en mémoire (CISC):

add adr1,adr2,adr3 (8+32x3=104 bits!)

En pratique, pour simplifier le contrôle du processeur, ce type

d’opérations est toujours fait avec des données préalablement placées

dans les registres du processeur (RISC):

add rx,ry,rz (8+6x3=26 bits)

Grâce à cette approche, 32 bits sont normalement suffisants pour

stocker une instruction complète. Pour des processeurs plus petits

(16 bits), on peut toujours réduire le nombre d’opérandes à deux:

move rx,rz

add ry,rz

Opérations arithmétiques et logiques

6

6

7

7

8

8

9

9

10

10

1

/

10

100%