Présentation - Polytechnique Montréal

3

Introduction

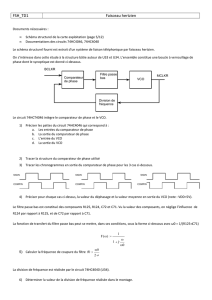

Un VCO est le module principal utilisé pour créer des horloges

avec une plage fréquentielle qui peuvent aller de quelques Hertz à

plusieurs Gigahertz

Applications : systèmes de télécommunications, les ordinateurs et

réseaux d’ordinateurs, multimédia, biomédicale, et d’autres

applications analogiques et numériques

Son importance nécessite l’utilisation d’une technique de test

fiable et efficace pour la détection des fautes

Dans le cadre de ce projet un VCO en anneau est conçu avec une

large plage fréquentielle pour une application biomédicale

1

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

1

/

30

100%