Architecture interne du microprocesseur 8086.

Jelassi Khaled Microprocesseurs 1

Architecture interne du

microprocesseur 8086.

Bus d'adresse:

Le 8086 utilise un bus d'adresse de 20 bits, ce qui lui permet d'atteindre 220 = 1M

cases mémoire de 1 octet chacune. Les 16 bits de poids faible du bus d'adresse

sont multiplexés avec les 16 bits du bus de données, alors que les 4 bits de poids

fort sont eux aussi multiplexés avec 4 bits de statut.

Organisation de l'espace adressable.

numéro de segment

(16 bits)

déplacement (16 bits)

0 0 0 0

adresse physique 20 bits

+

=

Jelassi Khaled Microprocesseurs 2

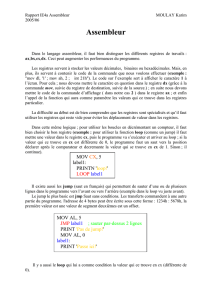

Mode d’adressage

Mode d’adressage

•Les instructions peuvent avoir 0, 1, ou 2 opérandes.

Exemples :

Instructions sans opérande: NOP,STI,CLI,PUSHF,CBW...;

Instructions avec une seule opérande: INC,DEC,NEG,NOT ....;

Instructions avec deux opérandes: CMP,ADD,MOV,LEA,XCHG,AND ......

Une opérande peut se trouver dans un registre du 8086, dans un octet,

dans un mot 16 bits ou dans un double mot 32 bits.

Les opérations peuvent avoir lieu:

entre un registre et un autre registre,

entre un registre et un octet ou un mot en mémoire mais pas entre 2 octets ou 2

mots en mémoire (il faut passer dans ce cas par un registre). Toutefois les

instructions de mouvement de chaînes d'octets effectuent "directement" le

transfert de mémoire à mémoire (octet par octet ou mot par mot), l'adressage se

faisant par les registres DS:SI et ES:DI.

Jelassi Khaled Microprocesseurs 3

Mode d’adressage

Les instructions de transfert

adressage registre à registre.

Exemple: MOV AX, BX ; opérandes 16 bit

ADD CH, DL ; opérandes 8 bits

adressage immédiat.

Exemples: MOV AX, 0A1EBH ; AX:= valeur hexa A1EB

ADD CL, 25 ; CL:= CL + 25

OR AH,11000000 ; forcer les 2 bits de fort poids de AH à 1

adressage direct.

Exemples: MOV BX,Total

MOV DX,ES:Nom

adressage indirect (ou basé).

Exemples: MOV AX,[BX]

MOV AX,[BP]

adressage indexé.

Exemple: MOV AX,Tab[SI]

adressage indirect indexé (ou basé indexé).

Exemples: MOV AX,[BX][SI] ; relatif a DS

MOV AX,[BP][SI] ;Relatif a SS

adressage basé indexé avec déplacement.

Exemple: MOV AX,Compte[BX][SI]

Jelassi Khaled Microprocesseurs 4

Les Principales Instructions de

l’assembleur

L’instruction LEA

Exemples: LEA BX,Tableau ;chargement de l’adresse de Tableau

LEA BX,Tableau[SI]

L'instruction XCHG.

Exemple: XCHG AX,Somme ;échange des contenus de AX et de Somme

Les instructions PUSH et POP

Exemple: PUSH SI ;empile le contenu de SI

Les instructions arithmétiques

Les instructions d'additionADD et ADC.

Exemples:

ADD AX,BX ;AX reçoit AX + BX

ADD AX,0F00H ;ces 2 instructions additionnent la

ADC DX,0 ;valeur immédiate 0F00H à la paire de

;registres DX:AX (32 bits).

Les instructions de soustraction SUB et SBB.

SUB AX,DX ;AX reçoit AX-DX

SBB SI,100 ;SI reçoit SI-100 - Carry

Jelassi Khaled Microprocesseurs 5

Les Principales Instructions de

l’assembleur

Les instructions de multiplication: MUL et IMUL

Exemples:

MUL CL ; AX:=AL * CL résultat sur 16 bits

IMUL CX ; DX:AX:= AX * CX résultat sur 32 bits non signe

Les instructions de division: DIV et IDIV

Exemples:

IDIV BX ;DX:AX est divisé par BX, le reste est dans DX et le quotient dans AX

DIV BL ;AX est divisé par BL, le reste est dans AH, le quotient dans AL.

Les instructions de décalage et de rotation

Les instructions de décalage gauche :SHL Opérande,Nombre

Opérande: Opérande = registre / case mémoire

Nombre: Nombre = soit la valeur 1, soit la valeur contenue dans CL

Les instructions de décalage droite :SHR Opérande,Nombre

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

1

/

21

100%