présentation OSTRE

Présentation action OSTRE 8 janvier 2002

1

OSTRE

Optimisation des Systèmes

Temps Réel Embarqués

Yves Sorel

http://www-rocq.inria.fr/~sorel/work/ostre

Présentation action OSTRE 8 janvier 2002

2

•Contexte

•Programme de recherche

•Logiciel

•Collaborations

•Enseignement

•Equipe

•Perspectives

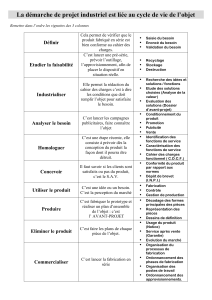

Plan

Présentation action OSTRE 8 janvier 2002

3

•Entre automatique et informatique : communauté du temps

réel et de l’architecture : depuis 1990 méthodologie AAA

•Applications : automobile et avionique (AEE, EAST),

robotique mobile (CyCab, SAFE), télécom (PROMPT)

•Algorithmes applicatifs : contrôle-commande, TSI

•Systèmes

•Réactifs : événement stimulus - opérations –événement réaction

•Temps réel : temps de réaction borné sinon conséquences catastrophiques :

contraintes latences (temps de réponse entrée-sortie) cadences (période entrée)

•Distribués : puissance calcul, modularité, câblage réduit

•Embarqués : minimisation des ressources

Contexte

Présentation action OSTRE 8 janvier 2002

4

Programme de recherche 4 axes

1) Modélisation des STRE : fondée sur la sémantique des

langages synchrones et le modèle matériel RTL

•Modèles de graphes pour algorithme (fonctionnalités) et

architecture (multicomposant et circuits intégrés spécifiques)

•Implantation transformation de graphes

2) Optimisation d’implantation temps réel

3) Génération automatique de code

4) Tolérance aux pannes

Présentation action OSTRE 8 janvier 2002

5

•Théorie des graphes, ordre partiel, automate

•Spécification Algorithme applicatif (parallélisme potentiel)

: hypergraphe orienté factorisé de dépendances de donnée (avec

ou sans précédence) et/ou de conditionnement entre opérations

(branchements), répétitif infini (réactif), répétitif fini (boucle)

•Vérification : langages Synchrones (ordre sur les événements)

•Spécification Architecture multicomposant (parallélisme

effectif) : graphe orienté de machines séquentielles : processeurs +

circuit intégrés spécifiques (ASIC, FPGA) + moyens de communication (mémoire

partagée, passage de message) : adapté à conception conjointe logiciel/matériel

Programme de recherche modélisation algorithme architecture

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

1

/

24

100%