ch6_pal_fpla

Les réseaux logiques programmables

•Introduction

•Principe des réseaux programmables

•Types des réseaux programmables combinatoires :

•PROM : Programmable Read-Only Memory

•PAL : Programmable Array Logic

•FPLA : Field Progmmable Array Logic

•Les réseaux programmables séquentiels

Chapitre 6

1. Introduction

•Chaque fonction logique de n variables peut être mise

sous la forme d’une somme de produits.

•Pour réaliser une telle fonction on a besoin :

– d’un ensemble d’opérateurs ET (portes AND)organisés sous

forme d’une matrice pour réaliser les produits.

– Un ensemble d’opérateurs OU (Porte OR) organisés sous forme

d’une matrice pour réaliser la somme.

CBACBACBAf ....),,(

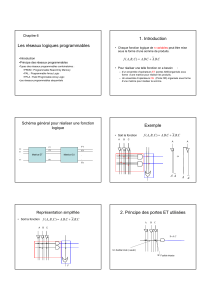

Schéma général pour réaliser une fonction

logique

Matrice ET Matrice OU

E0

E1

.

.

En

P1

P2

.

.

Pn

F1

F2

.

.

Fn

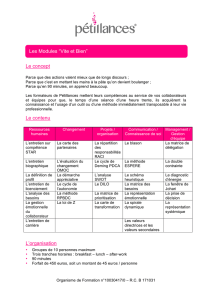

Exemple

•Soit la fonction

CBACBACBAf ....),,(

A B C AA

A

A

A

A

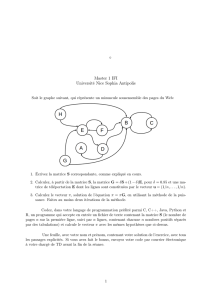

Représentation simplifiée

•Soit la fonction

CBACBACBAf ....),,(

F

A B C

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

1

/

33

100%