Distance en Y [µm] - Les Thèses de l`INSA de Lyon

N° d’ordre 2006ISAL0064 Année 2006

THÈSE

présentée devant

L’Institut National des Sciences Appliquées de Lyon

pour obtenir

LE GRADE DE DOCTEUR

Ecole doctorale : Électronique Électrotechnique Automatique (E.E.A.)

…………………………………………

Spécialité : Génie Electrique

par

Elena Ivanova DIMITROVA – FREY

Ingénieur de l’Université Technique de Sofia

Analyse et modélisation du JFET de puissance

en carbure de silicium en régime statique

Soutenue publiquement le 10 octobre 2006 devant la Commission d’examen

Jury

M. Gérard ROJAT Professeur UCB Lyon 1 Président

M. Hervé MOREL Directeur de recherche CNRS Directeur de thèse

M. Christian SCHAEFFER Professeur INP Grenoble Rapporteur

M. Stéphane LEFEBVRE Maître de conférence HDR ESCPI CNAM Rapporteur

M. Stéphane RAËL Maître de conférences Green – INPL Examinateur

Cette thèse a été préparée au Laboratoire CEGELY (Centre de Génie Electrique de Lyon)

UMR n° 5005 de l’INSA de Lyon, Futur Laboratoire Ampère.

2005

SIGLE ECOLE DOCTORALE NOM ET COORDONNEES DU RESPONSABLE

CHIMIE DE LYON

Responsable : M. Denis SINOU

M. Denis SINOU

Université Claude Bernard Lyon 1

Lab Synthèse Asymétrique UMR UCB/CNRS 5622

Bât 308

2ème étage

43 bd du 11 novembre 1918

69622 VILLEURBANNE Cedex

Tél : 04.72.44.81.83 Fax : 04 78 89 89 14

E2MC

ECONOMIE, ESPACE ET MODELISATION

DES COMPORTEMENTS

Responsable : M. Alain BONNAFOUS

M. Alain BONNAFOUS

Université Lyon 2

14 avenue Berthelot

MRASH M. Alain BONNAFOUS

Laboratoire d’Economie des Transports

69363 LYON Cedex 07

Tél : 04.78.69.72.76

Alain.bonnafous∂ish-lyon.cnrs.fr

E.E.A.

ELECTRONIQUE, ELECTROTECHNIQUE,

AUTOMATIQUE

M. Daniel BARBIER

M. Daniel BARBIER

INSA DE LYON

Laboratoire Physique de la Matière

Bâtiment Blaise Pascal

69621 VILLEURBANNE Cedex

Tél : 04.72.43.64.43 Fax 04 72 43 60 82

E2M2

EVOLUTION, ECOSYSTEME,

MICROBIOLOGIE, MODELISATION

http://biomserv.univ-lyon1.fr/E2M2

M. Jean-Pierre FLANDROIS

M. Jean-Pierre FLANDROIS

UMR 5558 Biométrie et Biologie Evolutive

Equipe Dynamique des Populations Bactériennes

Faculté de Médecine Lyon-Sud Laboratoire de Bactériologie BP

1269600 OULLINS

Tél : 04.78.86.31.50 Fax 04 72 43 13 88

E2m2∂biomserv.univ-lyon1.fr

EDIIS

INFORMATIQUE ET INFORMATION

POUR LA SOCIETE

http://www.insa-lyon.fr/ediis

M. Lionel BRUNIE

M. Lionel BRUNIE

INSA DE LYON

EDIIS

Bâtiment Blaise Pascal

69621 VILLEURBANNE Cedex

Tél : 04.72.43.60.55 Fax 04 72 43 60 71

EDISS

INTERDISCIPLINAIRE SCIENCES-SANTE

http://www.ibcp.fr/ediss

M. Alain Jean COZZONE

M. Alain Jean COZZONE

IBCP (UCBL1)

7 passage du Vercors

69367 LYON Cedex 07

Tél : 04.72.72.26.75 Fax : 04 72 72 26 01

MATERIAUX DE LYON

http://www.ec-lyon.fr/sites/edml

M. Jacques JOSEPH

M. Jacques JOSEPH

Ecole Centrale de Lyon

Bât F7 Lab. Sciences et Techniques des Matériaux et des

Surfaces

36 Avenue Guy de Collongue BP 163

69131 ECULLY Cedex

Tél : 04.72.18.62.51 Fax 04 72 18 60 90

Math IF

MATHEMATIQUES ET INFORMATIQUE

FONDAMENTALE

http://www.ens-lyon.fr/MathIS

M. Franck WAGNER

M. Franck WAGNER

Université Claude Bernard Lyon1

Institut Girard Desargues

UMR 5028 MATHEMATIQUES

Bâtiment Doyen Jean Braconnier

Bureau 101 Bis, 1er étage

69622 VILLEURBANNE Cedex

Tél : 04.72.43.27.86 Fax : 04 72 43 16 87

MEGA

MECANIQUE, ENERGETIQUE, GENIE

CIVIL, ACOUSTIQUE

http://www.lmfa.ec-lyon.fr/autres/MEGA/index.html

M. François SIDOROFF

M. François SIDOROFF

Ecole Centrale de Lyon

Lab. Tribologie et Dynamique des Systêmes Bât G8

36 avenue Guy de Collongue

BP 163

69131 ECULLY Cedex

Tél :04.72.18.62.14 Fax : 04 72 18 65 37

Introduction générale

Analyse et modélisation du JFET de puissance en carbure de silicium en régime statique

Thèse INSA de Lyon – CEGELY

Elena Ivanova DIMITROVA – FREY

1

Introduction générale

Dans le domaine de l’électronique de puissance, les dispositifs semi-conducteurs en

carbure de silicium se sont développés pour l’utilisation dans des conditions de haute

température, haute puissance, haute tension et haute radiation. Dans ces conditions, les

matériaux semi-conducteurs classiquement utilisés (notamment le silicium) sont souvent

moins performants. Le carbure de silicium (SiC) possède en effet des caractéristiques en

température et de tenue aux champs électriques bien supérieures au silicium.

Ces caractéristiques peuvent permettre le développement d’améliorations

significatives dans une grande variété d’applications et de systèmes. Les bonnes performances

en tenue en tension peuvent notamment permettre le développement de commutateurs forte

tension pour les applications de distribution d’électricité qui nécessitent des interrupteurs de

forte tension. Les capacités de fonctionnement sous hautes températures peuvent permettre de

développer des convertisseurs fortement intégrés et dans des environnements de hautes

températures comme dans l’aéronautique par exemple, mais aussi des dispositifs innovants

comme des limiteurs de courant. De même, ce matériau semble prometteur dans des

applications haute fréquence comme pour les radars ou les dispositifs de communication

radio-fréquences (RF).

De très grands progrès ont été accomplis pour obtenir des composants de bonne

qualité, il est toutefois nécessaire d’optimiser au mieux les structures et la conception des

composants en carbure de silicium afin de tirer la meilleure partie des qualités du matériau. Le

SiC possède un fort champ critique, il est toutefois nécessaire de veiller à ne pas dépasser les

valeurs maximale de champ électrique dans les structures. Ceci pourra être atteint notamment

en dimensionnant au mieux les protections périphériques des composants.

Introduction générale

Analyse et modélisation du JFET de puissance en carbure de silicium en régime statique

Thèse INSA de Lyon – CEGELY

Elena Ivanova DIMITROVA – FREY

2

Nous allons dans cette thèse regarder dans le premier chapitre les principales

caractéristiques des composants en SiC qui ont été présentés. Nous nous intéresserons plus

particulièrement aux transistors unipolaires de type JFET.

Nous allons notamment dans le deuxième chapitre tenter de comprendre le

fonctionnement d’un JFET présentant la caractéristique de posséder deux canaux dans lequel

le courant devra passer successivement. Ce type de structure semble être celle utilisée par le

fabricant de composants SiCED. Nos études seront basées sur le logiciel de simulation de

dispositifs MediciTMA.

Nous présenterons ensuite dans le troisième chapitre, un modèle de la résistance du

composant en fonction des paramètres physiques et géométriques du JFET. Nous

comparerons nos résultats avec ceux obtenus par le logiciel MediciTMA.

Enfin, nous regarderons dans le quatrième chapitre la tenue en tension en périphérie

des composants de puissance en étudiant plus particulièrement un type de protection

périphérique qui est l’extension latérale de jonction (JTE).

Le JFET est un composant disponible au niveau industriel. De très nombreuses études

ont été lancées mais les modèles simples du JFET ne sont pas adaptables. Ainsi nous voulons

étudier le transistor JFET en mode direct et inverse.

Liste des illustrations et des tableaux

3

Liste des illustrations et des tableaux

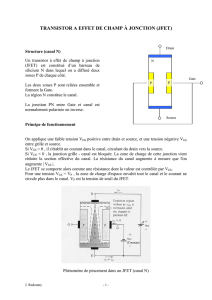

Figure 1-1 : Représentation schématique du canal non pincé dans une structure JFET à canal N avec le

sens d’orientation des axes (La structure présente une symétrie verticale. L’origine de l’axe des y est située

en haut du canal.)..........................................................................................................................................11

Figure 1-2 : Symboles du transistor JFET et convention de signes...............................................................12

Figure 1-3 : Répartition des porteurs dans le canal du JFET non polarisé (De chaque côté du canal la

jonction PN crée une zone de charge d’espace) ...........................................................................................13

Figure 1-4 : Conduction par champ électrique (dérive)................................................................................14

Figure 1-5 : Transistor JFET qui a la même zone de charge d’espace dans la coupe AA

′

(a) que la diode

PIN équivalente (b). La différence de potentiel de cette diode est notée [VA – VC ].....................................16

Figure 1-6 : a) Deux matériaux de type « p » et « n » sont mis ensemble pour former une jonction ; b) Un

champ électrique E apparaît suite à la nécessité d’aligner le potentiel à travers la jonction ......................17

Figure 1-7 : Région du canal d’un JFET qui montre la variation de la largeur de la zone de charge

d’espace le long du canal quand la tension de drain est beaucoup plus grande que la tension de source ..19

Figure 1-8 : Structure utilisée pour illustrer la modélisation ohmique dans la caractéristique statique du

canal du JFET. La simulation a été faite avec le logiciel éléments finis Medici pour VDS = 20 V et VGS = 0

V. (La largeur du canal est 2a = 2.6 µm, sa longueur est h=1 µm ; les autres paramètres sont

respectivement b = 0.2 µm et L = 2.6 µm.)...................................................................................................20

Figure 1-9 : ZCE dans un JFET : (a) Régime ohmique : le canal assure la conduction en zone neutre. (b)

Condition de pincement : Quand VDS augmente jusqu’à sat

DS

V, les ZCE des deux côtés du canal se

rencontrent au point de pincement pour y=l. (c) En régime de saturation le point de pincement pour y = l

′

se déplace vers la source...............................................................................................................................24

Figure 1-10 : Mobilité des électrons dans le canal vertical simulée par Medici...........................................25

Figure 1-11 : Réseau de caractéristiques électriques statiques ID =f(VDS ) à VGS donné d’un JFET canal N

pour Z = 1 µm (2a = 2.6 µm ; h = 1 µm ; VBI = 3 V ; ND=5

×

1015cm-3, µn = 400 V/cm.s ; VP = 4.81 V ;

on

DS

R= 1.56 Ω ; R0 = 0.14 Ω ; IDSS = 0.725 A ; VT0 = – 2.25 V) avec ses zones de fonctionnement simulé

avec le logiciel éléments finis Medici............................................................................................................27

Figure 1-12 : Lignes de courant au pincement avec l et l

′

............................................................................28

Figure 1-13 : Caractéristique de transfert normalisée d’une jonction abrupte d’un JFET (courbe bleue)

comparée avec la caractéristique racine carrée (courbe rose) ....................................................................30

Figure 1-14 : Caractéristique de transfert du JFET avec l’extraction du paramètre VT0 tracée à partir des

simulations Medici ........................................................................................................................................32

Figure 1-15 : Modèle statique d’un transistor JFET canal N sur une vue schématique du composant........34

Figure 1-16 : Caractéristiques I-V calculées à partir des équations SPICE (33) .........................................35

Figure 1-17 : Réseau de caractéristiques ID = f(VDS) en polarisation inverse tracées à partir des équations

SPICE............................................................................................................................................................36

Figure 2-1 : Structure schématique du JFET à canal vertical ......................................................................44

Figure 2-2 : Section transversale schématique du Trench JFET vertical 4H-SiC.........................................44

Figure 2-3 : Section transversale de la structure de base d’un trench JFET vertical 4H-SiC...................... 46

Figure 2-4 : Section transversale du dispositif..............................................................................................46

Figure 2-5 : (a) ID = f(VDS) pour VGS = 2 V à 25°C pour quatre VJFETs avec différentes tensions de seuil

VT0 ; (b) Caractéristiques de blocage à VGS = – 10 V pour les mêmes dispositifs (A VGS = – 20 V les

dispositifs bloquent 600 V à température ambiante)..................................................................................... 47

Figure 2-6 : ID = f(VDS) à VGS = 0 V pour des dispositifs normally-on et quasi-on ......................................48

Figure 2-7 : Influence de la largeur de la mesa sur le blocage en direct et la résistance spécifique à l’état

passant à température ambiante : la profondeur de la tranchée h est de 3 µm ; l’épaisseur de l’oxyde sur

les côtés TOX = 50 nm et le dopage de la couche épitaxiée ND = 1×1016 cm-3.............................................. 49

Figure 2-8 : Représentation schématique d’une demi-cellule d’un VJFET 4H-SiC......................................50

Figure 2-9 : Section transversale du VJFET .................................................................................................50

Figure 2-10 : Section transversale de la structure VJFET SiC .....................................................................53

Figure 2-11 : Section transversale du VJFET SiC.........................................................................................53

Figure 2-12 : Pouces de la source (1.5 µm) du VJFET SiC et la grille P+ implantée [13]...........................54

Figure 2-13 : Section transversale d’un JFET vertical en SiC [39]..............................................................54

Figure 2-14 : Vue de dessus du DI-JFET fabriqué [41]................................................................................57

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

130

130

131

131

132

132

133

133

134

134

135

135

136

136

137

137

138

138

139

139

140

140

141

141

142

142

143

143

144

144

145

145

146

146

147

147

148

148

149

149

150

150

151

151

152

152

153

153

154

154

155

155

156

156

157

157

158

158

159

159

160

160

161

161

162

162

163

163

164

164

165

165

166

166

167

167

168

168

169

169

170

170

171

171

172

172

173

173

174

174

175

175

176

176

177

177

178

178

179

179

180

180

181

181

182

182

183

183

184

184

185

185

186

186

187

187

188

188

189

189

190

190

191

191

192

192

193

193

194

194

195

195

196

196

197

197

198

198

199

199

1

/

199

100%