oscillateurs rf integres en technologie cmos/soi

4D-18

12èmes Journées Nationales Microondes, 16-17-18 mai 2001 - POITIERS

OSCILLATEURS RF INTEGRES EN TECHNOLOGIE CMOS/SOI

B. PARVAIS, M. GOFFIOUL, D. VANHOENACKER, J.-P. RASKIN

Université catholique de Louvain

Laboratoire d’Hyperfréquences - Place du Levant, 3

B-1348 Louvain-la-Neuve, Belgique

I. Introduction

Vu l’explosion actuelle du marché des télécommunications sans fil, il est nécessaire de développer des systèmes

performants peu encombrants, de faible coût et de faible consommation devant fonctionner à des fréquences de

plusieurs giga-Hertz. Dans ce cadre, la technologie CMOS est très attractive car, outre son faible coût de fabrication,

elle permet d’intégrer les parties analogiques et digitales d’un récepteur sur une même puce de silicium. D’autre part, la

technologie Silicium-sur-Isolant (SOI) permet d’augmenter les performances micro-ondes de circuits fonctionnant sous

de faibles tensions d’alimentation [1]. L’oscillateur présenté dans ce papier fonctionne à une fréquence de 5.8 GHz

sous une tension d’alimentation de 1.4 V et a été réalisé dans une technologie SOI de longueur de canal minimale de

0.25 µm. L’architecture choisie et le fonctionnement de l’oscillateur sont discutés dans la section suivante. Ensuite,

quelques résultats de mesures et simulations seront mis en évidence.

II. Fonctionnement de l’oscillateur

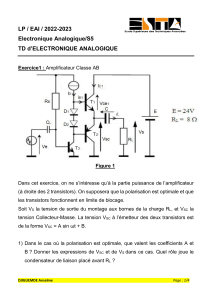

La structure étudiée utilise une boucle de rétro-action active pour entretenir l’oscillation créée dans un résonateur L-C

(Figure 1). Cette topologie étant différentielle, elle présente l’avantage de pouvoir se connecter directement à un

mélangeur de Gilbert, comme c’est fréquemment le cas dans les récepteurs RF.

Afin que le circuit oscille, il faut que les conditions suivantes soient vérifiées [2] :

í

ì

=+ℑ

≤+ℜ

0)(

0)(

ZpZam

ZpZae

La condition (1) indique que les transistors doivent fonctionner comme un générateur à résistance négative dont l’objet

est de compenser les pertes introduites par le résonateur. Le circuit de la Figure 1 vérifie cette condition car

m

g

d

g

Zae −

≈ℜ 2

)( et gd

m

g>> en pratique

Afin de s’assurer (1) en toutes circonstances, et de combler les déviations des paramètres technologiques, on choisit en

général la valeur de la transconductance avec un facteur de sécurité : gm=α/Rp (α=2..5, et Rp est la résistance

équivalente parallèle à l’inductance, modélisant les pertes de celle-ci).

Se référant à la Figure 1, la pulsation ω0 qui vérifie la condition (2) vaut :

ö

ç

ç

è

æ÷

ö

ç

è

æ

+

⋅

+⋅

=

21

21

3

1

2

0

CC

CC

CL

ω

. (3)

Figure 1 : Principe de l’oscillateur. Figure 2 : Circuit complet réalisé.

(1)

(

2

)

4D-18

12èmes Journées Nationales Microondes, 16-17-18 mai 2001 - POITIERS

Les capacités « naturelles » des transistors ont été utilisées pour implémenter la capacitance du résonateur. Dans (3),

3Cest donc négligeable par rapport à 21CC =. Ce procédé exige l’utilisation d’un modèle correct si l’on veut pouvoir

prévoir précisément par simulations la fréquence d’oscillation. Comme ces capacités sont fortement non-linéaires, le

facteur de qualité Qdu résonateur sera plus médiocre que dans le cas où des capacités de type métal-isolant-métal

(MIM) sont utilisées. Le bruit de phase de l’oscillateur est ainsi détérioré. En effet, la relation entre le bruit de phase

)( fL ∆à une distance f∆de la porteuse, et le

Q

du résonateur est (formule de Leeson) :

ö

ç

ç

ç

è

æ

÷

÷

ö

ç

ç

è

æ

∆

+=∆ 2

1

2

0

)1(

2

log10)(

RMS

V

f

f

F

Q

kT

RpfL

α

[dBc/Hz] (4)

où Rp est la résistance équivalente parallèle à l’inductance, VRMS est la tension moyenne, k, la constante de Boltzmann,

T, la température exprimée en Kelvin et

F

est le facteur d’excès de bruit (excess noise factor). Notons que l’équation

(4) se base sur un modèle linéaire invariant dans le temps du bruit de phase qui ne tient compte que du bruit blanc de

drain des dispositifs actifs : dfGFkTi mn ⋅⋅= 4

2. Elle met toutefois en évidence que le bruit de phase sera d’autant

meilleur que le facteur de qualité et la tension sont grands. Afin d’obtenir le plus grand facteur de qualité possible pour

les capacités, les MOSFETs ont été dessinés avec un grand nombre de petits doigts, permettant une diminution de la

résistance de grille.

Il est important de remarquer que les relations (1) et (2) sont des conditions nécessaires mais pas suffisantes

d’oscillation. En outre, la pulsation ω0 telle que donnée par (3) n’est pas nécessairement la pulsation ωR d’oscillation

en régime. Pour déterminer cette dernière, il faut tenir compte des non-linéarités de l’oscillateur. Néanmoins, ω0 ≈ ωR

si les pôles du demi-plan de droite sont à haut facteur de qualité, c’est à dire proche de l’axe imaginaire [3].

Le circuit complet réalisé est présenté à la Figure 2. En plus des éléments de la Figure 1, des sources de courant de

polarisation et un buffer de sortie y sont représentés. Ce buffer est nécessaire pour attaquer la charge de 50 Ω des

appareils de mesure. Il s’agit d’un amplificateur inverseur implémenté par un transistor monté en source commune.

Comme ce dernier est excité par un grand signal d’entrée (cfr. (5)), de nombreuses harmoniques seront produites et la

puissance de sortie est diminuée. Toutefois, vu qu’il est essentiellement déterminé par le facteur de qualité du

résonateur, le bruit de phase n’en souffre pas de manière notoire. Remarquons que l’amplitude du signal aux bornes de

l’inductance peut être approximée par [4], [5] :

eqtail RIV

π

4

≈ (5)

où tail

Iest le courant passant dans un transistor et eq

Rest la résistance équivalente parallèle du résonateur. Une analyse

non-linéaire est nécessaire pour une évaluation précise de l’amplitude.

Des améliorations peuvent être apportées à l’architecture en la symétrisant, afin d’exploiter pleinement les avantages de

la structure différentielle. Ainsi, il est préférable de connecter un buffer à chaque sortie et de n’utiliser qu’une source de

courant, éliminant ainsi les problèmes liés aux mauvais appariements. Ces améliorations, ainsi que l’utilisation d’une

source de courant externe et d’inductance intégrées à haut facteur de qualité (Q = 30…50) utilisant plusieurs couches de

métal ou des métaux épais, font l’objet d’un premier re-design. Les résultats de la section suivante, obtenus à l’aide du

circuit non-optimisé de la Figure 1, montrent les potentialités de la technologie SOI dans l’élaboration de circuits RF et

micro-ondes de faible consommation.

III. Mesures et simulations

Afin de simuler correctement les circuits en terme de fréquence d’oscillation, de puissance de sortie et de bruit de phase,

des modèles précis des dispositifs en jeu sont nécessaires. Les simulations présentées ici se basent sur un modèle

valable jusqu’à 40 GHz développé dans nos laboratoires [6]. Il se compose d’une partie extrinsèque incluant les effets

parasites importants à hautes fréquences et d’une partie intrinsèque basée sur un modèle non linéaire de charge. Les

simulations présentées ici ont été réalisées à l’aide du logiciel ELDO (type SPICE). Malheureusement, des simulations

de bruit de phase sont impossibles avec l’outil actuel de simulation.

Deux manières de concevoir des oscillateurs intégrés existent. La première [7] se base sur des techniques issues de la

micro-électronique basse fréquence : le résonateur est choisi en premier lieu, et la résistance négative est ensuite

dimensionnée pour combler les pertes du résonateur. La seconde méthode [8], propre à l’ingénierie micro-ondes, part

de la matrice de répartition des dispositifs actifs pour déterminer ensuite les éléments passifs. Les technologies

4D-18

12èmes Journées Nationales Microondes, 16-17-18 mai 2001 - POITIERS

actuelles permettant de réaliser des oscillateurs intégrés fonctionnant à très haute fréquence, donne au concepteur un

degré de liberté supplémentaire puisqu’il peut choisir les dimensions des dispositifs actifs. Par facilité, l’oscillateur

présenté ici a été dessiné en fixant tout d’abord les tailles des transistors. Les transistors nMOS utilisés comptent 12

doigts de 6.6 µm de large et 0.25 µm de long. Une inductance intégrée en spirale de 2.5 tours et de 4 nH est nécessaire

pour que l’oscillation ait lieu à la fréquence voulue. Il faut tenir compte des capacités vers le substrat que cette dernière

introduit pour avoir une idée précise des valeurs des capacités C1 et C2 de la Figure 1. Comme montré à la Figure 3,

les conditions d’oscillation (1) et (2) sont vérifiées pour le circuit de la Figure 2 à la fréquence de 5.4 GHz. Une analyse

transitoire permet de déterminer le comportement de l’oscillateur en régime : la fréquence est alors de 5.81 GHz (Figure

4). L’écart entre la pulsation de régime et celle déterminée par (2) est lié au faible facteur de qualité du résonateur ; il

reste néanmoins inférieur à 10%.

Les circuits, réalisés sur un substrat standard SOI de résistivité d’environ 20 Ω.cm, ont été mesurés sur la tranche de

silicium à l’aide d’une station sous pointes, les oscillateurs étant connectés directement à un analyseur de spectre

présentant une impédance d’entrée de 50 Ω. Le spectre obtenu pour une tension d’alimentation de 1.4 V est présenté à

la Figure 4 ; le courant total consommé vaut 3.44 mA. La faible puissance de sortie (-19 dBm) est liée à la basse

impédance de l’analyseur de spectre. Elle est relativement proche de la valeur annoncée par les simulation (Pout = -15

dBm). En pratique, dans les circuits de réception, la charge n’est pas si faible, puisqu’il s’agit généralement de la

capacité d’entrée d’un étage d’amplification. Le bruit de phase en fonction du décalage par rapport à la porteuse est

illustré à la Figure 5. Son origine est, comme expliqué précédemment, principalement liée au facteur de qualité de

l’inductance et à la forte non-linéarité des capacités MOS. En outre, le bruit en 1/f des MOSFETs contribue au bruit de

phase puisque la pente de la courbe de la Figure 5 est d’environ –30 dBc par décade, alors que dans (4), elle est de –20

dBc/décade.

Figure 3 : Partie réelle (O) et imaginaire (-) de l’impédance

vue aux bornes de l’inductance (simulation).

Figure 5 : Bruit de phase.

Figure 4 : Spectre mesuré de l’oscillateur.

4D-18

12èmes Journées Nationales Microondes, 16-17-18 mai 2001 - POITIERS

Les simulations numériques ont montré que l’amplitude du signal à l’entrée du buffer valait 0.5 V. Remarquons que

lorsque l’amplitude du signal est trop importante, les transistors entrent en régime linéaire et le signal de sortie est

distordu. La puissance de la raie principale diminue alors. La Figure 6 montre l’évolution de la fréquence d’oscillation

et la puissance de sortie en fonction de la tension de polarisation du circuit. L’augmentation de la tension

d’alimentation provoque l’augmentation de courant de polarisation, ce qui cause une variation des capacités MOS et

donc de la fréquence d’oscillation.

IV. Conclusions

L’oscillateur présenté dans ce papier montre les potentialités de la technologie SOI FD (Fully Depleted) dans les

circuits RF de basse puissance. En effet, grâce à l’utilisation de modèles précis des transistors MOS-SOI complètement

déplétés, des circuits fonctionnant sous de faible tension de polarisation et présentant des résultats comparables à ceux

de la littérature ont été réalisés [9]. Soulignons que ni les dispositifs en jeu, transistors et éléments passifs, ni

l’architecture du circuit n’ont été optimisés. Un second design dans une technologie SOI complètement (FD) et

partiellement déplétée (PD), est en phase de fabrication. L’oscillateur à 5.8 GHz consommant 4.8 mW et présentant un

bruit de phase de –87 dBc/Hz @ 1 MHz, permet au SOI de s’affirmer comme technologie bon marché de choix pour les

circuits intégrés de communication sans fil devant fonctionner à haute fréquence.

Références

[1] R. Gillon, J.-P. Colinge, D. Flandre, J.-P. Raskin, D. Vanhoenacker-Janvier, « Silicon-on-Insulator for RF and

microwave low-power applications », Workshop on New Technologies for RF Devices, London Heathrow,

May 21st, 1998.

[2] A. Khanna, J. Obregon, « Microwave Oscillator Analysis

», IEEE Transaction on Microwave Theory and

Techniques, Vol. MTT-29, No. 6, pp. 606-607, June 1981.

[3] N. Nguyen, R. Meyer, « Start-up and Frequency Stability in High-Frequency Oscillators

», IEEE Journal of

Solid-State Circuits, Vol. 27, No. 5, pp. 810-820, May 1992.

[4] A. Hajimiri, T. Lee, « Design Issue in CMOS differential LC Oscillators », IEEE Journal of Solid-State

Circuits, Vol. 27, No. 5, pp. 717-724, May 1999.

[5] J.J. Rael, A. Abidi, « Physical Processes of Phase Noise in Differential LC Oscillators », IEEE Custom

Integrated Circuits Conference,pp. 569-571, 2000.

[6] B. Iniguez et al., « Deep submicron DC to RF SOI MOSFET Characterization and modeling », ISDRS

Conference 2000.

[7] B. Razavi, RF Microelectronics. Upper Saddle River, NJ 07458 : Prentice Hall, 1998.

[8] G. Basawapatna and R. Stancliff, « A unified approach to the design of wide-band microwave solid-state

oscillators », IEEE Transaction on Microwave Theory and Techniques, Vol. MTT-27, pp. 379-385, May 1979.

[9] C. Hsiao, C. Kuo, Y. Chan, « 6.8 GHz monolithic oscillator fabricated by 0.35 µm CMOS technologies »,

Electronics Letters, 09/11/2000, Vol.36, No. 23, 2000.

Figure 6 : Puissance de sortie et fréquence d’oscillation

1

/

4

100%