Conception et test d`un VCO en anneau par des méthodes de test

1

Abstract— Dans cet article, un oscillateur en anneau tension contrôlé

(VCO) est présenté, ainsi que plusieurs méthodes de test pour tester ce

VCO. La topologie du VCO proposée permet d’obtenir une large plage

fréquentielle allant de 13 Hz à 407 MHz, ce qui est difficile à obtenir avec

un VCO conventionnel. Plusieurs méthodes de test sont exposées, mais trois

méthodes de test parmi celles-là ont été appliquées au VCO. Les deux

méthodes utilisées sont les tests statique et dynamique. La troisième

méthode est Idd RMS fonctionnel. Les résultats des trois méthodes de test

nous montre que le test Idd RMS fonctionnel offre un meilleur taux de

couverture, 74 %, en comparaison, respectivement des tests statique et

dynamique, 66 % et 68 %.

I. INTRODUCTION

n oscillateur tension-commandé (VCO) est considéré comme

un des modules les plus importants dans les circuits

analogiques et numériques et a reçu plusieurs attentions ces

dernières années. Son importance nécessite donc l’utilisation

d’une technique de test fiable et efficace pour la détection des

fautes.

La conception d'un oscillateur d'anneau exige de relier un

nombre impair d’inverseurs et de connecter la sortie du dernier

avec l’entrée du premier inverseur. Puisque la fréquence

d'oscillation est déterminée par le nombre d'étages et que le délai

dans chaque étage est très petit pour un inverseur, typiquement

les fréquences réalisées sont de plusieurs centaines de MHz à

GHz en technologie 0.8m. Pour réaliser une basse fréquence

en sortie, le nombre d'étages doit être très grand, mais beaucoup

de recherches ont été faite pour augmenter le délai dans chaque

étage au lieu d'augmenter le nombre d'étages [1, 2, 3]. Le VCO

en anneau proposé est dédié entre autre à une application

biomédicale. Elle demande une large plage fréquentielle et une

très faible fréquence d’horloge pour un émetteur ultrasonique.

Pour tester le VCO proposé, nous allons appliqués les

méthodes de test suivantes : le test de courant d’alimentation

[8], Les méthodes de test numérique (DFT) : le test statique et le

test dynamique [5, 6].

La section 2 présente la conception du VCO proposé. Les

différentes méthodes de test sont expliquées dans la section 3,

les tests et les résultats sont montrés dans la section 4, et la

conclusion se trouve dans la section 5.

II. CIRCUIT SOUS TEST

Un VCO en anneau conventionnel [3] est réalisé par des étages

de N inverseurs (N est un nombre impair), avec un mécanisme

de contrôle du courant passant dans ces inverseurs.

Habituellement, nous utilisons un transistor PMOS pour

contrôler le courant de la partie supérieur et un NMOS pour

contrôler le courant de la partie inférieure de l’étage inverseur.

Supposons que les capacités parasites Cg de la grille des

transistors de NMOS et de PMOS sont égaux, la fréquence

d’oscillation peut être définie tel que

τ

N

fosc

2

1

= (1)

où est le délai pour un étage, peut être défini par

ctrl

gosc

I

CV

=

τ

(2)

où Vosc est l'amplitude d'oscillation, et Ictrl est le courant de

contrôle. Des deux équations ci-dessus, nous pouvons en déduire

gosc

ctrl

osc CNV

I

f2

= (3)

D’après l’équation (3), il est évident de voir que la fréquence

d'oscillation peut être contrôlée par la variation du courant de

contrôle, en supposant que le nombre d'étages N et Cg sont fixes.

L'avantage de cette configuration est que la fréquence

d'oscillation peut varier dans une large plage fréquentielle en

changeant la valeur du courant de contrôle. Cependant, quand

Ictrl est très petit, il est difficile d’avoir le même courant entre la

partie supérieure et inférieure de l’inverseur. De plus, un faible

courant engendre une lente oscillation de tension et ne permet

pas d’avoir une amplitude d’oscillation maximum.

Dans [2], une méthode proposée consiste à ajouter une

résistance contrôlable à l'entrée de chaque étage. Cette méthode

produit une augmentation du délai, comme représenté dans la

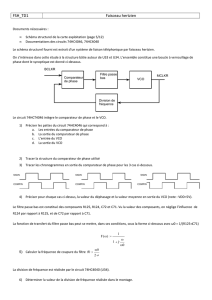

figure 1. Le délai de chaque étage peut être calculé à partir de la

figure 2, où gm est la transconductance de chaque inverseur et Cg

est la capacité parasite des transistors de NMOS et de PMOS.

N

Fig. 1 VCO avec résistance variable

Fig. 2 Approximation du délai pour un VCO avec une résistance contrôlable

Le délai de chaque étage peut être approximativement comme

suit :

m

Vmg

g

RgC )1(

+

=

τ

(4)

et la fréquence d’oscillation est :

)1(2 Vmg

m

osc RgNC

g

f+

= (5)

De l'équation (5) nous pouvons voir que la fréquence

d'oscillation peut être changée en variant la valeur de la

résistance RV, en supposant que Cg et gm sont constants. Ainsi

avec une grande valeur de RV, une basse fréquence d'oscillation

peut être obtenue en utilisant des transistors de faibles tailles et

moins d'étages d’inverseurs. La résistance contrôlable peut être

réalisée avec des transistors PMOS ou NMOS, comme proposé

R. Chebli (1069323), M.F. Navong (1270506)

Conception et test d’un VCO en anneau par des méthodes

de test numérique (DFT) et analogique

U

2

dans [4]. La résistance d'une porte de transmission peut être

contrôlée par ses tensions Vp et Vn. Habituellement Vp est égale

à VDD – Vn pour une raison de symétrie. Étant donné que le délai

de chaque étage est égal à la résistance de cet étage multipliée

par la capacité d'entrée de l’étage suivant, de même que la

méthode ci-dessus qui permet de changer le délai en ajoutant une

résistance contrôlable, on peut également obtenir un oscillateur

de fréquence variable en additionnant une capacité contrôlable.

Dû à la capacité supplémentaire CC connecté en parallèle avec la

capacité parasite Cg de l'inverseur, le délai pour un étage devient

m

Cg

g

CC

+

=

τ

(6)

et la fréquence d’oscillation est égale à

)(2 Cg

m

osc CCN

g

f+

= (7)

La capacité contrôlable peut être réalisée par un

transistor NMOS dont le substrat est connecté à la masse, sa

source et son drain sont reliés à une tension de contrôle (VC),

comme représenté sur la figure 3.

VDD

Vc

IN OUT

Fig. 3 Un étage du VCO avec une capacité contrôlable

Le diagramme bloc du VCO proposé, est montré dans la figure

4. Il est composé de cinq étages de cellule de délai, (D1 à D5)

reliées par une boucle et suivies d'un diviseur, et deux inverseurs

qui agissent comme un buffer. Afin d'obtenir une large plage

fréquentielle, la méthode conventionnelle est combinée avec la

méthode de résistance contrôlable [1]. Pour une faible fréquence

d'oscillation, un transistor NMOS est ajouté à chaque cellule de

délai agissant comme une capacité contrôlable.

Fig. 4 Schéma du VCO proposé

La figure 5 montre un étage du VCO proposé. Il se compose

d'un inverseur avec le courant contrôlé par un transistor NMOS

M1 en cascade, une porte de transmission comme résistance

contrôlable et un transistor NMOS comme capacité contrôlable.

En changeant seulement une tension de contrôle séparément, la

fréquence d'oscillation peut être changée selon l'équation (3), (5)

et (7) respectivement.

Vctr

VDD

Vp

Vn

M1

M2

M3

M5

M4 M6

Vc

Fig. 5 Cellule de délai combinant les méthodes de courant variable, résistance et

capacité

Comme mentionné ci-dessus, l'inconvénient du VCO

conventionnel est que lorsque le courant de contrôle est très

faible afin d’obtenir une oscillation de basse fréquence, cela

crée également une lente oscillation de tension et ne permet pas

d’avoir une maximum amplitude d’oscillation. En somme, le

niveau haut et le niveau bas du signal d’oscillation ne sont pas

égaux en basse fréquence. Afin d'éviter ce problème, un diviseur

par deux est utilisé à la fin de la boucle. Il est basé sur une

bascule flip flop dont sa sortie inversée est redoublée à son

entrée, comme représenté sur la figure 5. La bascule est activée à

chaque front montant de l'entrée. Par conséquent, le duty cycle

est toujours de 50 %, indépendamment de la fréquence. En

outre, elle divise la fréquence d'oscillation par deux. Dans le cas

où on opère en basse fréquence, les temps de montée et de

descente sont relativement lents, ce qui empêche au diviseur de

fonctionner correctement. Pour remédier à ce problème, on

utilise un circuit de buffer qui se compose d'un ensemble

d'inverseurs. Les inverseurs après la bascule sont utilisés dans le

même but. Finalement, un multiplexeur, basé sur une porte de

transmission et un signal de contrôle, est utilisé pour contrôler le

fonctionnement du VCO en basse ou en haute fréquence, en

utilisant ou non le diviseur, respectivement.

III. METHODES DE TEST

Étant donné que le VCO est un circuit analogique, les défauts

qui peuvent affecter un circuit analogique sont répartis dans

deux types de fautes :

Les fautes catastrophiques « hard fault », ce sont des fautes dues

à des défauts aléatoires pouvant provoquer des courts-circuits ou

des circuits ouverts. Ils peuvent engendrer des comportements

complètement différents du fonctionnement

normal du VCO. Les fautes catastrophiques sont les suivantes :

a) court-circuit : Grille-Drain, Grille-Source, Drain-Source, b)

circuit-ouvert : Grille, Drain, Source. En pratique, les fautes

catastrophiques de court-circuit sont plus probables que les

autres fautes.

Les fautes paramétriques « soft fault » sont des fautes dûes à

des déviations des paramètres du circuits crées par les variations

du processus de fabrication (W, L, R et C). Elles engendrent des

déviations des sorties en dehors de leur intervalle de tolérance.

Dans la littérature, plusieurs méthodes de test sont décrites pour

le test d’un oscillateur en anneau dont on en résume les

principales dans cette partie :

- Test de courant d’alimentation :

En mode fonctionnel «Operating Idd Test »

En mode non-fonctionnel « Non-operating Idd Test »

- VCOBIST

3

- Méthodes de test numérique (DFT) :

Test statique avec VCO reconfigurable

Test dynamique avec VCO reconfigurable

A. Test de courant d’alimentation :

En mode fonctionnel «Operating Idd Test »

Le test de courant d’alimentation en mode fonctionnel est basé

sur la mesure de la valeur moyenne du courant nominale

d’alimentation du VCO en anneau correct. Cette valeur est

comparée avec la valeur RMS du courant d’alimentation d’un

VCO fautif [8]. Pour réaliser cette méthode de test, il faut laisser

osciller le VCO pendant quelques s et mesurer la valeur RMS

du courant nominal. En injectant des fautes catastrophiques, si la

faute est détectée, on doit obtenir une valeur de courant proche

de quelques nA, sinon si la faute n’est pas détectée, on doit

obtenir une valeur proche de la valeur RMS nominale dans un

intervalle de tolérance de ± 20 %.

En mode non-fonctionnel « Non-operating Idd Test »

Le test de courant d’alimentation en mode non-fonctionnel est

basé sur la mesure de la valeur RMS du courant nominale

d’alimentation (de l’ordre de quelques nA) du VCO en anneau

correct. Cette valeur est comparée avec la valeur RMS du

courant d’alimentation d’un VCO fautif (supérieur à 1 A) [8].

Pour réaliser cette méthode de test, il faut laisser osciller le VCO

pendant quelques ns et puis ramener Vctrl à zéro, afin de le

mettre à l’état de repos. La valeur RMS du courant a été

enregistrée pour les cas du circuit correct et circuit fautif.

B. VCOBIST

Le VCOBIST effectue ses mesures de synchronisation à l'aide

de deux oscillateurs en anneaux, l’un (OSC #2) fonctionne

légèrement plus rapide que l'autre (OSC #1), mais les deux

fonctionnent plus lentement que le signal de sortie du VCO sous

test mesuré. Le système de BIST mesure le temps entre deux

fronts d'horloge successifs du signal de sortie de VCO sous-test,

avec un degré de précision élevé [9, 10]. En prenant les mesures

répétées (4k) du même signal, on peut voir si cette période

change dans le temps (jitter). Les spécifications pour les deux

oscillateurs en anneau #1 et #2 utilisés, doivent être respectées

afin de maintenir la précision exigée dans une plage de quelques

psec. La figure 6 montre que OSC #1 commence avec le front

montant de la période de mesure et OSC #2 commence à la fin

de la période de mesure.

Fig.6 Principe de mesure du jitter

Ensuite, nous surveillons la relation de phase entre les deux

oscillateurs tout en gardant le nombre de cycle d’oscillation qui

se produit avant que les deux signaux se coïncident.

La relation de fréquence f = f#1 - f#2 constitue principalement

la résolution du VCOBIST. Les oscillateurs d'anneau utilisés

doivent montrer une fonctionnalité stable et fonctionner à une

faible variation de phase (jitter). Afin d’obtenir les résultats

corrects, on doit les calibrer avant chaque période de mesure.

Les composants de BIST les plus sensibles qui sont les

oscillateurs en anneaux doivent être identiques.

Fig.7 VCOBIST

La figure 7 nous montre le diagramme bloc du VCOBIST. Le

détecteur de coïncidence détecte les fronts montants des signaux

de sortie des deux oscillateurs en anneaux. Il y a deux

compteurs qui comptent les périodes de chaque oscillateur.

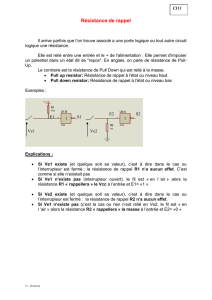

C. Méthodes de test numérique (DFT)

Le principe est basé sur le concept de reconfiguration [5, 6].

Ce concept est proposé pour tester le VCO comme une fonction

analogique en mode test. Par contre, la technique présentée ici

propose de modifier le VCO original pour qu'il fonctionne

comme une structure numérique en mode test.

Le principe est la modification du circuit original permet de

l’activer en deux modes distincts : a) le mode fonctionnel, dans

lequel le VCO fonctionne normalement, b) le mode test, dans

lequel le VCO est reconfiguré en une structure numérique

permettant un test efficace.

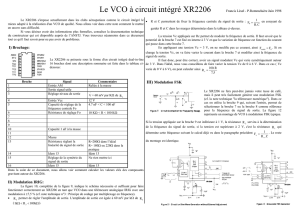

D’après la figure 8, le VCO se compose de trois parties: (i)

l’étage d’entrée de contrôle de délai, (ii) les étages de gain et

(iii) le buffer de sortie. Un étage de gain dans le domaine

analogique correspond à un inverseur dans le domaine

numérique. Par conséquent, du point de vue numérique, nous

pouvons voir le VCO comme une interconnexion d’inverseurs

et des éléments de contrôle de délai.

L'idée est de modifier la structure initiale de sorte que le VCO

fonctionne comme une chaîne d’inverseurs en mode test. La

méthode propose d'ouvrir la boucle de l’oscillateur en anneau et

de rebrancher le noeud flottant résultant au noeud de la sortie de

l'étage de contrôle.

L’implémentation du DFT illustré à la figure 9, implique alors

simplement d'ajouter deux interrupteurs supplémentaires.

Selon la valeur du signal de test, le VCO reconfigurable

fonctionne comme un oscillateur en anneau à délai contrôlé

(Test = 1) ou comme une série d'inverseurs (Test = 0).

Fig. 8 Représentation symbolique du VCO

4

Fig.9 Principe du VCO reconfigurable

1) Test statique avec VCO reconfigurable :

La méthode de test numérique statique consiste à appliquer un

test booléen classique (ou tension statique), qui permet à

vérifier la fonctionnalité logique du circuit. Plus précisément, le

VCO en mode test (Test = 0) correspond à une série de cinq

inverseurs. Le test booléen consiste donc à vérifier qu’un 0

logique en entrée donne un 1 logique en sortie et inversement.

2) Test dynamique avec VCO reconfigurable :

Le test dynamique est basé sur l'évaluation de la propagation de

délai des chaînes d’inverseurs au lieu des tensions statiques [5].

Le principe du test dynamique consiste à appliquer un signal

carré dissymétrique sur l'entrée des chaînes d’inverseurs et à

mesurer le temps au niveau bas du signal de sortie comme

illustré sur la figure 10. Ce temps mesuré a été identifié comme

un paramètre de test efficace de la caractérisation du

comportement dynamique et statique de logique du VCO. En

effet, ce temps peut être exprimée comme : tL(OUT) = tH(IN) +

(tLH - tHL), où tLH et le tHL sont les délais de propagation

dynamique.

Fig.10 Test dynamique avec VCO reconfigurable

Le stimulus de test d'entrée est un signal carré dissymétrique qui

permet la distinction entre les niveaux bas et haut des signaux

d’entrée et de sortie du VCO reconfigurable. La décision de

déclarer un circuit fautif ou correct est prise en comparant la

valeur mesurée à la valeur nominale selon un intervalle de

tolérance de ± 10 %.

IV. TEST ET RESULTATS

A. Test fonctionnel

La conception a été faite en utilisant la technologie 0.8m

5V/400V CMOS/DMOS fourni par Dalsa Semiconductor. La

simulation a été effectuée avec Spectre sous la plateforme

CADENCE. La figure 11 montre respectivement les

caractéristiques transitoires du VCO à la fréquence de 13 Hz et

de 407 MHz. La figure 11(a) montre la courbe transitoire

symétrique de la sortie après avoir utilisé le diviseur, à la

fréquence très basse de 13 Hz, ce qui est très difficile d’obtenir

avec d'autres VCOs.

(a)

(b)

Fig. 11 Réponse transitoire du VCO : (a) à 13 Hz

avant et après diviseur, (b) à 407 MHz

La figure 12 montre le résultat de la simulation de la fonction de

transfert, fréquence de sortie en fonction de Vctrl. En fixant, la

tension de contrôle de la résistance et de la capacité et en

augmentant Vctrl, la fréquence atteint 407 MHz. La courbe de la

tension de contrôle de 1V à 1.8V, correspondant à la fréquence

d'oscillation de 70 MHz à 300 MHz, est presque linéaire. La

fréquence centrale mesurée est de 225 MHz et correspond à un

Vctrl de 1.5V.

Fig. 12 Fréquence en fonction de la tension Vctrl (DFT)

B. Méthodes de test numériques

1) Test numérique statique

En appliquant ce test pour notre VCO décrit dans le paragraphe

III-C, nous avons injectés des fautes catastrophiques unitaires

pour chaque transistor MOS de la chaîne de cinq étages

d’inverseurs de la figure 13.

La faute de court-circuit est modélisée par une résistance de

100 et la faute de circuit ouvert est modélisée par une

résistance de 100M. Étant donné que l’impédance de la grille

d’un transistor MOS est presque infinie, la faute de circuit

ouvert de la grille du transistor MOS (faute non probable) est

modélisée par un interrupteur, permettant d’isoler la grille du

circuit, comme montré sur la figure 14.

Fig. 13 Schéma de l’étage de gain du VCO (Fig.13 agrandi en annexe)

5

Fig. 14 Circuit ouvert sur la grille du transistor M7

La figure 15 montre une faute équivalente avec une résistance de

100M utilisé comme modèle de faute source ouverte et drain

ouvert. Cette faute est comptée comme une seule faute dans la

liste des fautes. Donc, le nombre de fautes est réduit à cinq

fautes au lieu de six par étage d’inverseur.

Fig. 15 Faute équivalente : Source ouverte M8-Drain ouvert M9

Résultats du test numérique statique

Nous avons obtenu 56 fautes détectées sur un total de 85 fautes

(3 transistors par étages d’inverseurs et 5 fautes par transistor).

Ce qui nous permet de déterminer un taux de couverture

TCbooléen = 66 %.

Nous avons appliqué deux vecteurs de test en entrée du VCO :

0 et 1 logique. Le 0 logique correspond à Vss et le 1 logique

correspond à Vdd.

Fig. 16 Faute détectée court-circuit drain-source M7

Fig. 17 Faute non détectée du court-circuit drain-source sur le transistor M9

Pour les deux vecteurs de test utilisés dans la figure 17, la faute

de court-circuit drain-source sur M9 n’est pas détectée. Lorsque

Vin = 5V, Vout = 5V (1 logique) et inversement.

On doit noter que les fautes de court-circuit sur le transistor de

contrôle de courant (contrôle de délai) comme par exemple sur

M9, ne sont pas détectées (fautes difficiles à détecter), car pour

le test statique, ce transistor fonctionne comme un interrupteur

qui transfert le VSS à la source du transistor NMOS de l’étage

d’inverseur.

2) Test numérique dynamique

Pour ce test, nous avons injecté un signal carré dissymétrique de

fréquence de 1MHz, avec un niveau haut de 400ns et un niveau

bas de 600ns (figure 18), et nous avons mesuré le paramètre de

test qui est le temps au niveau bas tL(OUT) du signal de sortie :

tL(OUT) = tH(IN) + (tLH - tHL)

= 400 + (2.4-2.75)

tL(OUT) = 399.65ns

Comme mentionné dans le paragraphe III-C, Ce paramètre de

test servant à la caractérisation du comportement dynamique,

nous permet de prendre la décision de déclarer si la faute est

détectée ou non. Cette décision est prise en comparant la valeur

mesurée à la valeur nominale selon l’intervalle de tolérance de ±

10 %, ce qui correspond à ± 40ns de tL(OUT) calculé pour notre

application.

Fig.18 Signal d’entrée et signal de sortie du circuit correct

Résultat de test numérique dynamique

Nous avons détecté 58 fautes, Comme prévu, le test numérique

dynamique permet de détecter quelques fautes qui ne sont pas

détectées par le test numérique statique. Les deux fautes

supplémentaires détectées sont les fautes de circuit ouvert sur la

source du transistor de contrôle. Le taux de couverture augmente

de TCbooléen = 66 % à TCdyn = 68 %

Fig.19 Faute détectée source ouverte M8 drain ouvert M9

Dans l'analyse détaillée des résultats de la détection de défaut,

on note que la plupart de ces défauts non détectés sont des court-

circuits drain-source dans les transistors de contrôle du courant.

Ces défauts sont considérés comme des fautes difficiles à

6

6

7

7

8

8

9

9

10

10

1

/

10

100%

![III - 1 - Structure de [2-NH2-5-Cl-C5H3NH]H2PO4](http://s1.studylibfr.com/store/data/001350928_1-6336ead36171de9b56ffcacd7d3acd1d-300x300.png)