Stratégie d`alimentation des Systèmes sur Puce RF très

Stratégie d’alimentation des Systèmes sur Puce RF

très faible consommation

Thomas COULOT, Frédéric HASBANI

Power Management Design Team

STMicroelectronics

850, rue Jean Monnet

F38920 Crolles - France

Estelle LAUGA, Jean-Michel FOURNIER

IMEP-LAHC UMR 5130

3, rue Parvis Louis Néel – BP 257

Minatec

F38016 Grenoble Cedex 1 - France

Email : thomas.coulot@grenoble-inp.org

Résumé

Ces travaux concernent l’étude d’une stratégie

d’alimentation adaptée aux systèmes sur puce RF très faible

consommation. Une modélisation de la partie bande de base

de l’émetteur est réalisée afin de montrer la relation entre les

performances et les variations de l’alimentation. Le résultat

sera utilisé pour mettre en place une architecture

d’alimentation optimisée. Enfin, les résultats de mesure d’un

bloc de cette future architecture, réalisé en technologie

CMOS 90nm de STMicroelectronics, sont présentés.

1. Introduction

Un réseau de capteurs sans fils [1], également appelé

Wireless Sensor Network (WSN) est constitué d'éléments

communicants qui forment les nœuds du réseau. La

communication des capteurs entre eux ou des capteurs

avec la base de collecte de données s'opère par ondes

radio.

Chaque nœud intègre différents composants : une

source d’énergie, des périphériques constitués de capteurs

ou d’actionneurs, un processeur et un émetteur-récepteur.

L’autonomie énergétique de ces nœuds peut être assurée

par des cellules photovoltaïques, permettant à chaque

nœud de créer et de disposer de leur propre énergie (une

batterie intégrée en assure le stockage).

Ce type de réseau intelligent de capteurs sans fils

autonomes en énergie peut être configuré pour avoir

plusieurs fonctions. Chaque nœud a une mission propre,

fonction des périphériques qu'il contient. Il peut

communiquer les informations concernant cette mission, à

l'ensemble du réseau ou à la tête de réseau.

Si la base collectant les données est reliée à Internet,

on peut alors imaginer un grand nombre d'applications

dans de multiples domaines : industriel, domotique

(Figure 1), aide à la personne...

La technologie a un rôle central dans le rendement

énergétique et dans le coût du système complet. Un effort

important est donc mis sur le développement d'une

technologie ultra-basse consommation. Ces attentes

forcent aussi à changer la façon de réaliser les émetteurs-

récepteurs RF, partie gourmande en énergie, et notamment

leurs stratégies d'alimentation [2].

Ce papier s’organise de la façon suivante. Tout

d’abord, le défi à relever dans la mise en place d’une

stratégie d’alimentation pour de telles applications est

présenté. Puis, la méthodologie de conception est décrite.

La dernière partie présente un régulateur de tension

linéaire innovant conçu et testé en technologie CMOS

90nm de STMicroelectronics.

Figure 1. Exemple de réseau de capteurs sans fils.

2. Une stratégie d’alimentation : un réel défi

La Figure 2 représente les différents blocs composants

les Systèmes sur Puce RF très faible consommation. On y

trouve le(s) régulateur(s) de tension qui alimente(nt)

ensuite les blocs analogiques, RF ainsi que les blocs

numériques.

Batterie Régulateur(s)

de tension

Blocs

analogiques (RF)

et numériques

Vbat Vdd

Systèmes sur Puce très faible consommation

Figure 2. Schéma bloc des Systèmes sur Puce RF très

faible consommation.

Afin de limiter la consommation du système sur puce,

les régulateurs de tension doivent consommer le moins

possible. Les blocs analogiques et RF doivent également

être les moins gourmands possibles en énergie. Les

fonctions RF présentent donc des architectures optimisées

en termes de consommation, ce qui les rend par contre

plus sensibles aux variations de l’alimentation.

L’alimentation de ces blocs doit donc être la moins

bruitée possible sur une large bande de fréquence. Elle

doit avoir un PSR (« Power Supply Rejection ») le plus

élevé possible. Le PSR définit la capacité que présente un

système à minimiser l’impact des variations de la tension

d’alimentation sur le signal de sortie.

2.1 Une demande particulière

Afin de limiter leur consommation, les systèmes RF

fonctionnent dans différents modes. Selon les besoins, les

blocs analogiques, RF et numériques sont soit éteints, soit

en veille, soit actifs [3]. Cette technique réduit

considérablement la consommation de l’émetteur-

récepteur sans dégrader ses performances. Les trois

principaux modes de fonctionnement sont :

• « Power Down Mode » : seuls les blocs qui

permettent le réveil sont actifs, le reste du

système est éteint.

• « Idle Mode » : tout le système est alimenté, il est

à l’écoute d’un signal qui le réveillerait.

• « Active Mode » : émission/réception des

données. Ce mode est utilisé seulement lors de

transactions de données.

Ces modes de fonctionnement impliquent la mise en

place d’une stratégie d’alimentation dynamique avec un

réveil rapide. En effet, le temps de démarrage des

régulateurs doit être inférieur au temps de transmission

d’une trame de données par exemple.

De plus, une application à très faible consommation

comme les réseaux de capteurs sans fils doit présenter

également un faible coût. La puce RF doit donc avoir une

surface la plus faible possible et ne pas nécessiter de

composants externes (pas de capacité de découplage ni

d’inductance pour les régulateurs). L’architecture de

l’alimentation doit être constituée de régulateurs adaptés,

de faibles surfaces et sans composants externes.

2.2 Etat-de-l’Art des stratégies d’alimentation

Actuellement, les régulateurs linéaires de type Low

Drop Out (LDO) sont connectés directement à la batterie

afin d'alimenter les parties RF, analogiques et numériques

[4] [5] [6] (Figure 3). Les avantages d'une telle solution

sont la faible taille de ce genre de circuit et leur faible

coût. Cependant, leur rendement énergétique peu élevé

handicape sévèrement l'autonomie et donc le temps de vie

de la batterie.

LDO LDO

Fonctions

RF Numérique

Vbat

Figure 3. Etat-de-l’Art des stratégies d’alimentation.

Sachant que les fonctions RF représentent environ

50% de la consommation au sein d'un nœud [1], la mise

en place d'une stratégie intelligente dédiée à la RF devient

cruciale pour atteindre l'objectif principal, l'augmentation

de l'autonomie.

2.3 Un réel manque de stratégie

La conception d’un émetteur-récepteur RF est réalisée

à partir d’un cycle de conception en V (méthodologie

descendante/montante). Ainsi, elle permet à différents

groupes au sein d’un même projet d’évoluer du « besoin »

au « produit ». A partir d’un cahier des charges, une

analyse fonctionnelle est effectuée, ce qui permet un

découpage en différentes fonctions. Par la suite, ces

fonctions donneront lieu à des architectures distinctes.

Une fois l’architecture décidée, les concepteurs analysent

chaque bloc unitaire, les conçoivent et les simulent.

Le problème est que l’architecture de l’alimentation

n’est pas étudiée lors de l’analyse fonctionnelle. Les

spécifications et les répartitions des différentes contraintes

n’apparaissent pas dans le cahier des charges. Le

concepteur va donc réaliser et simuler les fonctions RF en

utilisant une alimentation idéale. Il ne prendra pas en

compte les bruits apportés par l’alimentation, l’impédance

ramenée par l’alimentation ni les perturbations des blocs

voisins qui passent par ces chemins.

L’étude d’une stratégie d’alimentation devient donc

indispensable dans la conception de circuits très faibles

consommations afin d’obtenir la meilleure optimisation,

les meilleurs compromis et performances possibles.

3. Proposition d’une stratégie

Pour faciliter la phase de conception des futurs

émetteurs-récepteurs et de leur stratégie d’alimentation,

une démarche de modélisation a été définie et pourra être

appliquée lors de la conception des circuits. Il est

envisageable d’obtenir un modèle spécifique à

l’architecture du circuit tout en étant réutilisable lorsque

certains paramètres (technologiques ou dimensionnels)

seront modifiés.

3.1 Motivations de l’action de modélisation

Bien qu’il soit possible de simuler individuellement

les circuits constituant un émetteur-récepteur, ils ne

peuvent pas être analysés dans le cadre d’un

fonctionnement complet en émission ou en réception en

restant au niveau transistor pour une analyse de réjection

d’alimentation par exemple. En effet, le nombre de nœuds

et la complexité des équations des modèles transistors font

que les capacités des stations de travail s’avèrent

insuffisantes pour ce genre de tâche.

Il est donc à ce niveau nécessaire de procéder à la

modélisation du circuit afin de garantir que le

comportement soit conforme à nos attentes.

Cette démarche de modélisation va permettre d’une

part une vérification rapide de l’ensemble des propriétés

des circuits créés (conception montante) et, d’autre part, la

détermination rapide des principales caractéristiques des

blocs d’alimentation afin qu’ils respectent les

spécifications (conception descendante).

3.2 Modélisation descendante

Dans le cas de la modélisation descendante, la

première étape consiste à modéliser les chemins entrée-

sortie des blocs RF de la chaîne. A ces premiers modèles,

on y ajoute tous les chemins d’alimentation, c’est-à-dire

les chemins VDD-entrée, VDD-sortie, VDD-polarisations

internes mais également les chemins inverses afin

d’obtenir un modèle complet (illustré par la Figure 4).

MODELE

BLOC RF

POLAR

IN OUT

VDD VDD

Figure 4. Modélisation du bloc RF.

Pour résumer, les blocs modélisés possèdent quatre

accès : une entrée/sortie IN, une entrée/sortie OUT, une

entrée/sortie VDD et une entrée/sortie POLAR. Ces

modèles sont ensuite simulés ensemble pour aboutir à une

modélisation système qui permet de concevoir une

stratégie d’alimentation adaptée et de vérifier que le

système satisfait les objectifs qui avaient été fixés.

La modélisation qui a été mise en œuvre a ainsi pour

but de vérifier le comportement du circuit RF (analyse

montante) et de concevoir la stratégie d’alimentation

(analyse descendante). On pourra ainsi, lors de

simulations au niveau système, vérifier l’impact d’une

alimentation bruitée sur le reste de la chaîne réception-

émission et sur ses performances RF.

3.3 Langage de modélisation utilisé [7]

Le langage de modélisation utilisé est le Verilog-A.

C’est une extension du langage de modélisation Verilog

(IEEE 1364, « Verilog Hardware Description

Language »). Il permet une modélisation exclusivement

analogique des circuits. Parmi les propriétés de ce

langage, on peut lister les fonctions de bruit, le contrôle

exercé sur le pas calcul du simulateur ou encore les

nombreuses fonctions mathématiques permettant une

adaptation des équations pour concorder avec les

caractéristiques observées.

Le langage Verilog-A présente l’avantage d’être

utilisable avec des simulateurs tels que Spectre-RF de

Cadence et avec Eldo-RF de Mentor Graphics.

3.4 Exemple de modélisation : la bande de base

L’objectif de la modélisation en Verilog-A des circuits

travaillants en bande de base est de permettre de retrouver

le même comportement du circuit que celui simulé au

niveau transistor mais de manière plus rapide. Parmi les

propriétés à retrouver dans le modèle, on peut notamment

citer les impédances d’entrée et de sortie des blocs RF

mais également l’impédance des blocs vu par

l’alimentation, leur consommation en courant en fonction

du signal et des perturbations de l’alimentation, la

variation de l’entrée et de la sortie des blocs en fonctions

des ondulations de l’alimentation et les réjections de

l’alimentation de chaque bloc.

L’architecture du circuit travaillant en bande de base à

modéliser est la suivante :

PMA

VGA

FLT

RXBB

Figure 5. Architecture de la bande de base étudiée.

Elle est constituée d’un amplificateur (« Post Mixer

Amplifier » (PMA)), un filtre passe-bande et d’un

amplificateur à gain variable (VGA).

La première vérification concerne le comportement

« petit signal » des modèles de ces trois blocs. La Figure 6

représente le comportement des modèles du PMA, du

filtre et du VGA et la simulation des schémas des mêmes

blocs au niveau transistor quand l’alimentation est excitée

en régime « petit signal ». Il faut en effet pouvoir garantir

que les modèles intègrent bien les réjections propres de

chaque bloc.

1 100 10K 1M 100M

1100 10K 1M 100M

1 100 10K 1M 100M

1 100 10K 1M 100M

Fréquence (Hz) Fréquence (Hz)

Fréquence (Hz) Fréquence (Hz)

Figure 6. Comparaison du régime « petit signal » des

blocs avec leurs modèles.

La vérification suivante consiste à s’assurer que le

comportement en régime transitoire « grand signal » des

différents blocs soit respecté. La Figure 7 représente le

comportement temporel de chaque bloc quand

l’alimentation varie sinusoïdalement avec une amplitude

de 50mV et à la fréquence de 10MHz.

-0.02

-0.015

-0.01

-0.005

0

0.005

0.01

0.015

0.02

2.00E-06 2.20E-06 2.40E-06 2.60E-06 2.80E-06 3.00E-06

0.57

0.58

0.59

0.6

0.61

0.62

0.63

0.64

0.65

2.00E-06 2.20E-06 2.40E-06 2.60E-06 2.80E-06 3.00E-06

0.56

0.57

0.58

0.59

0.6

0.61

0.62

0.63

0.64

0.65

2.00E-06 2.20E-06 2.40E-06 2.60E-06 2.80E-06 3.00E-06

1.14

1.16

1.18

1.2

1.22

1.24

1.26

2.00E-06 2.20E-06 2.40E-06 2.60E-06 2.80E-06 3.00E-06

2.0 2.2 2.4 2.6 2.8 3.0

1.14

1.26

1.16

1.18

1.20

1.22

1.24

Temps (μs)

VDD (V)

1.14

1.16

1.18

1.2

1.22

1.24

1.26

2.00E-06 2.20E-06 2.40E-06 2.60E-06 2.80E-06 3.00E-06

2.0 2.2 2.4 2.6 2.8 3.0

1.14

1.26

1.16

1.18

1.20

1.22

1.24

Temps (μs)

VDD (V)

2.0 2.2 2.4 2.6 2.8 3.0

2.0 2.2 2.4 2.6 2.8 3.0

2.0 2.2 2.4 2.6 2.8 3.0

Temps (µs)

Temps (µs)

Temps (µs)

PMA (V)FLT (V)VGA (V)

0.57

0.58

0.59

0.60

0.61

0.62

0.63

0.64

0.65

-0.02

-0.015

-0.01

-0.005

0

0.005

0.01

0.015

0.02

0.56

0.57

0.58

0.59

0.60

0.61

0.62

0.63

0.64

0.65

Verilog-A

Transistor

Verilog-A

Transistor

Verilog-A

Transistor

Figure 7. Comparaison du régime transitoire des blocs

avec leurs modèles Verilog-A.

Les résultats obtenus avec les simulations des modèles

Verilog-A démontrent la fiabilité et l’efficacité des

modèles. Le gain de temps réalisé (simulation 300 fois

plus rapide) permet de diminuer la durée de

développement des alimentations et de permettre la

simulation complète du système lors de sa conception.

Une fois la chaîne RF complètement modélisée, il

suffira de proposer plusieurs stratégies d’alimentation et

de choisir, selon les contraintes et les performances, la

plus adaptée à l’application.

4. Conception d’un régulateur innovant

Dans les stratégies d’alimentation actuelles, les

régulateurs de tension de type Low Drop Out (LDO)

servent d'interface entre la batterie et les circuits intégrés.

Le but du régulateur linéaire est de délivrer en sortie une

tension stabilisée fixe, et ce quel que soit le courant

demandé par le système en aval et quelle que soit la

tension d'alimentation fournie par la batterie en amont.

Pour gagner sur l'autonomie de la batterie, on cherche à

repousser la limite basse d'alimentation du régulateur, ce

qui revient à définir un minimum entre la sortie

d'alimentation en dessous duquel l’application ne soit plus

alimentée. De ce fait, on utilise une catégorie de

régulateur qui se caractérise par une faible chute de

tension d'où son appellation de régulateur Low Drop Out.

Afin d’augmenter le rendement énergétique du

système, un régulateur à découpage est souvent cascadé

en amont de ces régulateurs linéaires. Le principal

inconvénient de cette architecture est le bruit engendré par

les commutations du régulateur à découpage. Cette

architecture impose donc au régulateur linéaire d’avoir un

fort PSR sur une large bande de fréquence (~20MHz).

Cependant, les régulateurs linéaires classiques ne peuvent

pas rejeter de telles ondulations à des fréquences aussi

élevées à cause de leur structure intrinsèque.

Un régulateur innovant [8] constitué de plusieurs

boucles de rétroaction est présenté. Il assure une réjection

de 45dB jusqu’à 100MHz avec seulement 47nF de

capacité de découplage.

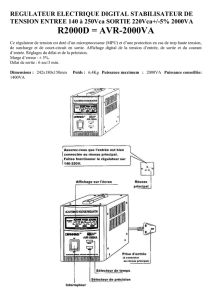

4.1 Architecture du régulateur

La Figure 8 décrit l’architecture du régulateur linéaire

conçu pour maintenir une faible sensibilité aux variations

de la tension d’alimentation aux hautes fréquences. Pour

compenser le régulateur sans sacrifier la réjection de

l’alimentation ou augmenter la consommation, une

seconde boucle de rétroaction est introduite, ce qui permet

de stabiliser le gain et d’augmenter la bande passante tout

en conservant la stabilité. L’utilisation d’une charge

dupliquée sous forme de modèle équivalent à la charge

réelle permet d’améliorer les performances. En effet, cette

boucle locale va permettre une estimation du bruit à

laquelle la charge réelle va être soumise et ainsi, l’étage

de sortie sera piloté en fonction de cette estimation d’où

une meilleure réjection sur la charge réelle.

Figure 8. Architecture du LDO.

Une boucle principale (

A

1

et

P

5

) régule la tension de

sortie

V

reg

chargée par la charge

Z

load

. La seconde

boucle de rétroaction (

A

2

et

P

4

) est utilisée pour

augmenter le PSR à hautes fréquences, à travers une

réplique miniaturisée de la charge

Z

replica

. Cette seconde

boucle permet de réinjecter les variations de

l’alimentation dans la boucle de contrôle du LDO, ce qui

diminue l’impact de ces variations sur le nœud de sortie.

Pour obtenir une réjection optimale, la tension aux

bornes du réplica

V

rep

et la tension aux bornes de la

charge

V

reg doivent réagir de la même manière aux bruits

de l’alimentation. Le réplica doit ressembler exactement à

la charge : comportement tension/courant, bruits…

A hautes fréquences, la boucle du réplica, qui est plus

rapide que la boucle principale, prend le contrôle pour

stabiliser le LDO et rejeter les ondulations de la tension

d’alimentation. A basses fréquences, les deux boucles

fonctionnent et sont en compétition pour stabiliser le

LDO. Une petite différence entre la charge et le réplica

combinée à une différence de gains entre les boucles a

pour conséquence une variation de la réjection en DC.

Pour éviter la variation de PSR à basses fréquences, un

filtre passe-haut [9] est ajouté dans la boucle du réplica,

ce qui permet de filtrer les variations de l’alimentation,

l’offset DC et les composantes basses fréquences de

V

rep , correspondant à la différence entre la charge et le

réplica. Grâce à ce filtre, le PSR reste constant à basses

fréquences, indépendant de la ressemblance entre la

charge et le réplica et il dépend uniquement du gain de

l’amplificateur.

4.2 Résultats de mesure

Le LDO a été fabriqué en technologie CMOS 90nm

STMicroelectronics. L’aire totale du LDO est de

0.0088mm ² sans le circuit de type bandgap pour générer

la tension de référence. Une capacité extérieure de 47nF

est utilisée pour stabiliser le LDO. Elle possède une

résistance équivalente en série de 32mΩ et une inductance

équivalente en série de 600pH.

La Figure 9 montre la carte de test avec le socket RF

utilisé.

Figure 9. Carte de test du LDO.

Le régulateur fonctionne avec une tension d’entrée

allant de 1.4V à 3.3V et la tension de sortie est de 1.2V.

La tension de déchet du régulateur est donc de 200mV. Le

LDO consomme 200µA avec une alimentation de 2V.

La charge à alimenter est un oscillateur contrôlé en

tension (VCO). Il est intégré sur la même puce que le

LDO. Le filtre passe-haut implémenté est de type GmC.

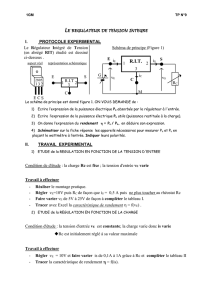

Pour mesurer la réjection de l’alimentation, un

analyseur de réseau HP8753D a été utilisé pour mesurer le

niveau de signal à l’entrée et à la sortie du LDO. On

mesure le paramètre S21 en balayant la fréquence par un

signal sinusoïdal sur la bande souhaitée. La réjection

d’alimentation en est déduite. Le signal sinusoïdal a une

amplitude de 25mV pour éviter de perturber le point de

polarisation du LDO. La comparaison entre le PSR

mesuré et simulé est montrée sur la Figure 10. Le LDO

possède une réjection de 45dB à 100MHz. A partir de

20MHz, le PSR commence à augmenter à cause des pôles

internes de la structure et de la résonnance de la capacité

de découplage.

100K 1M 10M 100M

-45

-50

-55

-60

-65

-70

-75

-80

Fréquence (Hz)

PSR (dB)

Figure 10. Comparaison entre la réjection simulée et

mesurée.

5. Conclusion

Dans ce papier, une stratégie permettant de prendre en

compte, au stade de la conception, l’effet des

perturbations induites par l’alimentation des différents

blocs constituant un émetteur-récepteur RF très faible

consommation est présentée. Une modélisation de la

chaîne RF permet de simuler le système complet. A partir

de ces simulations, les liens entre les performances et les

variations de l’alimentation sont établis et des

architectures d’alimentation optimisées et adaptées en sont

déduites.

Un composant central de cette architecture, un

régulateur de tension linéaire LDO, est aussi présenté. Ce

régulateur linéaire innovant dédié à l’alimentation d’une

fonction RF (VCO) a été réalisé en technologie CMOS

90nm. Il assure 45dB de réjection jusqu’à 100MHz avec

seulement 47nF de capacité de découplage.

Références

[1] M. Camus, "Architecture de réception RF très faible coût et

très faible puissance. Application aux réseaux de capteurs et

au standard ZigBee", PhD thesis, Feb. 2008.

[2] V. Raghunathan, C. Schurgers, S. Park and M. Srivastava,

"Energy-Aware Wireless Microsensor Networks", IEEE

Signal Processing magazine (March 2002) pp. 40-50.

[3] A. Sinha and A. Chandrakasan, "Dynamic Power

Management in Wireless Sensor Networks", IEEE Design &

Test of Computers (2001) pp. 62-74.

[4] A. Liscidini, M. Tedeschi and R. Castello, "A 2.4GHz

3.6mW 0.35um quadrature front-end RX for ZigBee and

WPAN applications", IEEE ISSCC (2008) pp. 370-371.

[5] R. Van Langevelde, M. Van Elzakker and D. Van Goor, "An

Ultra Low Power 868/915MHz RF Transceiver for Wireless

Sensor Network Applications", IEEE RFIC (2009) pp. 113-

116.

[6] A. Minhas, M. Faheem and M. Azeem, "Ultra Low Power

Small Size RF Transceiver Design for Wireless Sensor

Networks", Int. Conf. on Collaboration Technologies and

Systems (2011) pp. 290-295.

[7] http://www.eda.org/verilog-ams/htmlpages/overview.html;

Accelera Verilog Analog Mixed-Signal Group.

[8] T. Coulot, E. Rouat, J.-M. Fournier, E. Lauga and F.

Hasbani, "High Power Supply Rejection (PSR) Low Drop-

out Regulator for Ultra Low Power Radiofrequency

Functions", IET Electronics Letters (2011) pp. 1117-1118.

[9] T. Coulot, E. Rouat and F. Hasbani, "Replica Compensated

High PSR LDO", French Patent submitted in June 2011.

1

/

5

100%