r1 - Free

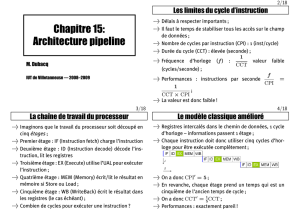

Architecture de l’ordinateur - Pipeline

Copyright © F. Muller

2004 Ch5 - 1 -

Plan

Ch1 - Introduction

Ch2 - Structure de l’ordinateur

Ch3 - Modèle de Programmation

Ch4 - Conception des Processeurs

Ch5 - Pipeline

Ch6 - Parallélisme d’instructions

Ch7 - Systèmes Mémoire

Ch8 - Mémoires Caches

Ch9 - Mémoire Virtuelle

Ch10 - Systèmes Multiprocesseurs

Ch5 - 2 -

Copyright © F. Muller

2004

Pipeline

Introduction

Pipelining

Aléas d’instructions

Prédire le temps d’exécution

Forwarding du résultat

Architecture de l’ordinateur - Pipeline

Copyright © F. Muller

2004 Ch5 - 3 -

Introduction

Objectifs

Comprendre le pipelining

Calculer le temps de cycle d’un processeur pipeliné

Décrire le forwarding de résultat et expliquer la manière

dont il affecte le temps d’exécution

Calculer le temps d’exécution de petits segments de code

sur processeurs pipelinés avec forwarding du résultat

Introduction

Les premiers ordinateurs

Chaque instruction (étapes de lecture, décodage, lecture du fichier de registre,

calcul, …) était entièrement achevée avant d’exécuter la suivante

Inconvénient : chaque étapes restent inopérantes la plupart du temps

De nos jours

Pipeline : Recouvrir l’exécution de plusieurs instruction afin de réduire le temps

d’exécution d’une séquence d’instructions

Inconvénient : nécessite quelques ajouts matériels au processeur mais la

vitesse des instructions exécutées est augmentée

Architecture de l’ordinateur - Pipeline

Copyright © F. Muller

2004 Ch5 - 4 -

Pipelining – Principe (1/3)

Processeur non Pipeliné

Exécution des étapes pas à pas

Extraction

de l’instruction

Décodage

de l’instruction

Lecture

des registres

Exécution

de l’instruction

Écriture du résultat

dans les registres

12345

temps

Architecture de l’ordinateur - Pipeline

Copyright © F. Muller

2004 Ch5 - 5 -

Pipelining – Principe (2/3)

Extraction

de l’instruction

Latch

EI

Processeur Pipeliné

Division du chemin de données en

plusieurs sections

Ajout de « latches » entre chaque

section

Une section s’appelle un étage

Chaque étage possède une latence

d’un cycle horloge

1 cycle

d’horloge

Décodage

de l’instruction

Latch

DI 1 cycle

d’horloge

Lecture

des registres

Latch

LR 1 cycle

d’horloge

Exécution

de l’instruction

Latch

EX 1 cycle

d’horloge

Pipeline à 5 étages

1 cycle

d’horloge

Écriture du résultat

dans les registres

ER

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

1

/

28

100%