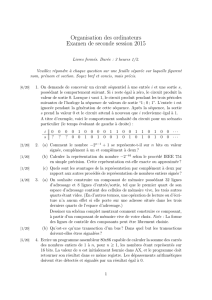

l`assembleur sur simulateur

L'assembleur sur Simulateur 1 M. DALMAU IUT de Bayonne

L'ASSEMBLEUR

SUR SIMULATEUR

L'assembleur sur Simulateur 2 M. DALMAU IUT de Bayonne

LE PROCESSEUR

Les registres

Le processeur possède 8 registres de 32 bits :

R0 à R6 registres de 32 bits pouvant être utilisés comme opérandes dans toutes les instructions ou comme

pointeurs pour désigner un opérande en mémoire par son adresse.

SP pointeur de pile utilisé par les procédures et les instructions relatives à la pile (PULL, PUSH).

La mémoire est constituée de 1K mots de 32 bits.

Les opérandes

Le processeur traite les opérandes suivants :

- Entiers naturels sur 32 bits

- Entiers relatifs sur 32 bits en complément à 2

- Caractères en code ASCII

- Chaînes de caractères de codes ASCII

- Pointeurs constitués d'une adresse sur 10 bits.

JEU D'INSTRUCTIONS

Notation : pour simplifier les descriptions ci-dessous on choisira de désigner par :

RG un registre quelconque (R0 à R6 ou SP)

[RG] un registre quelconque (R0 à R6 ou SP) utilisé pour désigner un opérande en

mémoire par son adresse (pointeur). Seuls les 10 bits de faible poids de RG sont

utilisés comme adresse.

[RG+d] un registre quelconque (R0 à R6 ou SP) utilisé pour désigner un opérande en

mémoire par son adresse (pointeur). La valeur d (de 0 à 1023) désigne le

déplacement par rapport à cette adresse. L'opérande est donc le mot de la mémoire

dont l'adresse est obtenue en faisant: contenu des 10 bits de faible poids de RG + d.

RG n'est pas modifié.

Var un opérande en mémoire désigné par son nom (adresse)

Val une valeur sur 16 bits (– 32767 à +32767).

Instructions de déplacements de données

LD dest, source opération : dest ← source

dest peut être RG ou [RG]

source peut être RG ou [RG] ou [RG+d] ou Var ou Val

ST source, Var opération : Var ← source

source peut être RG ou

[RG]

LEA dest, Var opération : dest ← adresse en mémoire de la variable désignée.

dest peut être RG ou [RG]

Remarque : cette instruction permet d'initialiser un registre comme pointeur sur une variable. Elle sera,

en particulier utilisée pour initialiser le pointeur de pile (SP) sur le sommet de pile en début de

programme (voir plus loin).

SWAP oper opération : échange les 16 bits de fort poids et les 16 bits de faible poids

de l'opérande qui peut être RG ou [RG] ou [RG+d] ou Var.

L'assembleur sur Simulateur 3 M. DALMAU IUT de Bayonne

Instructions arithmétiques

ADD op1 , op2 opération : op1 ← op1 + op2

SUB op1 , op2 opération : op1 ← op1 - op2

MUL op1 , op2 opération : op1 ← op1 * op2 : Multiplication d'entiers relatifs

MULU op1 , op2 opération : op1 ← op1 * op2 : Multiplication d'entiers naturels

DIV op1 , op2 opération : op1 ← op1 / op2 : Division d'entiers relatifs

DIVU op1 , op2 opération : op1 ← op1 / op2 : Division d'entiers naturels

Dans les 6 instructions précédentes op1 peut être RG ou

[RG]

op2 peut être RG ou [RG] ou [RG+d] ou Var ou Val

INC oper opération: oper ← oper + 1

L'opérande peut être RG ou [RG] ou [RG+d] ou Var.

DEC oper opération: oper ← oper - 1

L'opérande peut être RG ou [RG] ou [RG+d] ou Var.

NEG oper opération: oper ← - (oper)

L'opérande peut être RG ou [RG] ou [RG+d] ou Var.

Remarque : les instructions arithmétiques, à l'exception de NEG, positionnent les indicateurs de

débordement des entiers naturels et relatifs du registre d'état de l'unité de traitement.

Instructions logiques

OR op1 , op2 opération : op1 ← op1 OU op2

AND op1 , op2 opération : op1 ← op1 ET op2

Dans ces deux opérations

op1 peut être RG ou

[RG]

op2 peut être RG ou [RG] ou [RG+d] ou Var ou Val

NOT oper opération: oper ← COMPLEMENT oper

L'opérande peut être RG ou [RG] ou [RG+d] ou Var.

Instruction de comparaison

CMP op1 , op2 opération : compare op1 à op2

op1 peut être RG ou [RG]

op2 peut être RG ou [RG] ou [RG+d] ou Var ou Val

Ne produit aucun résultat autre que celui de positionner les indicateurs du registre d'état de l'unité de

traitement utilisés par les instructions de branchement.

Instructions de décalage

SHR oper opération : oper est décalé à droite (décalage logique).

SHL oper opération : oper est décalé à gauche (décalage logique).

SAR oper opération : oper est décalé à droite (décalage arithmétique).

SAL oper opération : oper est décalé à gauche (décalage arithmétique).

ROR oper opération : oper est décalé à droite (décalage cyclique).

ROL oper opération : oper est décalé à gauche (décalage

cyclique).

Dans ces instructions l'opérande peut être RG ou [RG] ou [RG+d] ou Var.

DEBER est l'indicateur de débordement des entiers naturels du registre d'état de l'unité de traitement.

0

DEBER

0

DEBER

DEBER

DEBER

DEBER

0

DEBER

L'assembleur sur Simulateur 4 M. DALMAU IUT de Bayonne

Instructions de branchement (rupture de séquence)

JMP etiq opération : branchement inconditionnel.

Bxx etiq opération : branchement conditionnel.

Dans ces instructions etiq doit être une étiquette (instruction où aller).

Se référer à la table ci-dessous pour les différentes conditions de branchement :

condition comparaison

d'entiers naturels

comparaison

d'entiers relatifs

égal

différent

inférieur

inférieur ou égal

supérieur

supérieur ou égal

débordement

BEQ

BNE

BLTU

BLEU

BGTU

BGEU

BDEBU

BEQ

BNE

BLT

BLE

BGT

BGE

BDEB

Instructions relatives à la pile

PUSH oper opération : empile oper. (SP ← SP-1 puis Mem(SP) ← oper)

PULL oper opération : dépile oper. (oper ← Mem(SP) puis SP ← SP+1)

Dans ces instructions l'opérande peut être RG ou [RG] ou [RG+d] ou Var.

Instructions d'appel et retour de sous programmes

CALL etiq opération: appel du sous-programme référencé par etiq.

etiq doit être une étiquette (instruction de début de la procédure)

RET opération : retour de sous-programme.

RET Val opération : retour de sous-programme avec vidage de la pile.

La valeur en opérande indique le nombre de mots en sommet de pile à

enlever (ignorer) après le retour. Ces mots correspondent à des paramètres

mis dans la pile avant l'appel du sous-programme et que l'on désire enlever à

la fin.

Instruction de contrôle

HLT opération : arrêt du processeur

Instructions relatives à l'unité d'échange (Entrées / Sorties)

IN oper, port opération : oper ← octet du registre de l'unité d'échange désigné par son n°.

OUT oper, port opération : octet du registre de l'unité d'échange désigné par son n° ← oper.

Dans ces instructions oper peut être RG ou [RG], port est un entier naturel désignant le n° de port de

l'unité d'échange. Seuls les 8 bits de faible poids de oper sont utilisés.

L'assembleur sur Simulateur 5 M. DALMAU IUT de Bayonne

L'ASSEMBLEUR DU SIMULATEUR

La syntaxe d'une ligne d'assembleur est :

[etiquette:] [COP [operande1 [, operande2]]] [; commentaire]

Où un terme noté entre crochets est facultatif.

• Une étiquette est un mot qui ne doit comporter aucun caractère défini comme délimiteur par le

langage ( ' " ; , [ ] ) ni d'espaces. Elle peut contenir des caractères accentués et elle doit être

terminée par :

• Le COP est l'un des codes définis précédemment il peut indifféremment être écrit en minuscules ou

en majuscules.

• Un commentaire débute au ; et se termine à la fin de la ligne. Il peut contenir tous les caractères sauf

des guillemets ( " ).

Désignation des opérandes dans les instructions autres que celles de rupture de

séquence :

Registre : On met le nom du registre qui contient l'opérande (en majuscules ou minuscules)

exemple : LD R0,r1 ; R0 ← R1

Valeur immédiate : On met la valeur de l'opérande selon la forme :

décimal 123 ou –4 valeur de 0 à 655355 ou –32767 à 32767

hexadécimal $1a ou $ffa3 valeur sur 16 bits (4 digits hexadécimaux au maximum)

binaire %01110010 valeur sur 16 bits (16 chiffres binaires au maximum)

ASCII 'a' code ASCII d'un caractère

ATTENTION : Le caractère placé entre ' ne peut être " ni ; car ce sont des délimiteurs définis dans le

langage (délimiteurs de chaîne de caractères et de commentaire)

exemples : LD R1,$ff03 ; R1 ← FF03 en hexadécimal

LD R2,'A' ; R2 ← code ASCII de 'A'

Direct : On met le nom de la variable

exemples : LD R0,var1 ; R0 ← contenu de var1

ST R2,var2 ; var2 ← contenu de R2

ATTENTION : Un nom de variable doit commencer par une lettre et ne comporter aucun caractère

défini comme délimiteur par le langage ( ' " ; , [ ] ). Le compilateur distingue les majuscules et les

minuscules et accepte les caractères accentués. De plus un nom de variable ne doit pas pouvoir être

confondu avec un nom de registre ni être le mot clé STACK.

Indirect : Le registre désigné contient l'adresse de l'opérande (seuls les 10 bits de faible poids du

registre sont pris en compte). On met le nom du registre entre crochets.

exemples : LD R0,[SP] ; R0 ← contenu de la mémoire à l'adresse contenue dans SP

LD [R1],12 ; mémoire à l'adresse contenue dans R1 ← 12

LD [R1],r3 ; mémoire à l'adresse contenue dans R1 ← contenu de R3

LD [r1],var ; mémoire à l'adresse contenue dans R1 ← contenu de var

ST [R2],var2 ; var2 ← contenu de la mémoire à l'adresse contenue dans R2

LD [sp],[R1] ; mémoire à l'adresse contenue dans SP ← contenu de la

mémoire à l'adresse contenue dans R1

Désignation des opérandes dans les instructions de rupture de séquence :

On met l'étiquette qui désigne l'instruction à laquelle on doit aller (le nom seul de l'étiquette sans les :).

exemple : BNE début

6

6

7

7

8

8

9

9

10

10

11

11

12

12

1

/

12

100%