Mise en oeuvre de la simulation mixte électronique / TCAD

MISE EN OEUVRE DE LA SIMULATION MIXTE ELECTRIQUE/TCAD

POUR DECLOISONNER L'ENSEIGNEMENT DE LA MICROELECTRONIQUE

Jean-Marc Gallière, Jérôme Boch

Pôle CNFM de Montpellier

Polytech'Montpellier, Université de Montpellier II

{galliere, boch}@polytech.univ-montp2.fr

RESUME

Dans un parcours classique d'école d'ingénieur en microélectronique, les élèves acquièrent des

compétences aussi bien en physique du composant qu'en conception analogique et numérique des circuits

intégrés. Généralement, pour illustrer ces enseignements, à chacun de ces cours est associé une série de

travaux pratiques mettant en œuvre des outils informatiques de simulation et/ou de conception. Cependant,

au cours du temps, cette approche mène à un cloisonnement des enseignements et pose subrepticement des

barrières conceptuelles dans l'esprit des élèves. Cet article propose une série de TPs où les élèves sont

amenés à associer des simulations TCAD électrique et SPICE. A l'aide de ces TPs, l'enseignant pourra

souligner l'interdépendance de ces outils mais avant tout montrer que les enseignements associés sont

fortement liés et partagent des objectifs communs.

Mots clefs - TCAD, Simulation mixte, Transistor MOS

1- INTRODUCTION

Durant la conception d'un circuit intégré, le flot de données traverse plusieurs couches logicielles.

Généralement, à chacune de ces couches logicielles est associé un niveau d'abstraction (Fig. 1). D'autres

outils logiciels permettent de passer d'une couche à une autre. Par exemple, la description d'un circuit intégré

au niveau comportemental en VHDL ou Verilog peut se retrouver au niveau de description logique après la

phase dite de synthèse. Les couches inférieures sont composées des niveaux électrique et physique. Au

niveau électrique le circuit ne comporte plus des portes logiques mais des transistors et leurs

interconnections. Au niveau physique, le transistor est maintenant considéré dans son aspect physique; nous

sommes dans l'univers du TCAD (Technology Computer Aided Design).

faible

comportemental

VHDL/Verilog

élevé

physique electrique logique

SPICE TCAD

Niveau d'abstraction

synthèse

Fig. 1: Les différents niveaux d'abstraction

Dans son domaine de spécialisation, l'ingénieur en conception de circuits intégrés utilise des outils de

simulation pour un niveau d'abstraction donné. Par exemple, l'outil de vérification fonctionnelle Modelsim

[1] fournit un environnement performant pour la simulation et la mise au point d'ASIC ou de FPGA. Cet

outil supporte plusieurs langages de description tels que le Verilog et le VHDL. Dans ce cas, ce sont les

niveaux d'abstraction "comportemental" et "logique" qui sont adressés. Pour le niveau électrique, les

principaux simulateurs sont HSPICE [2], Spectre [3] et Eldo [4]. Pour le niveau physique, deux outils

dominent le marché du TCAD. Il s'agit de Silvaco [5] et Sentaurus (ex. ISE) [6].

Toute cette hiérarchie d'outils de conception CAO conduit involontairement à un fort cloisonnement des

enseignements mais surtout empêche les élèves d'avoir une vue globale de la conception des circuits

intégrés. Pour cela, nous proposons dans ce TP de montrer aux élèves le lien qu'il existe entre la simulation

physique et électrique au travers de la simulation mixte proposé par l'outil Silvaco. Mais avant tout, l'intérêt

de cette démarche est d'impliquer dans cette séquence pédagogique des enseignants issus de chacun de ces

PCM

P15

deux "mondes". De cette manière, l'enseignement devient plus cohérent et par conséquence la perception

transversale des contenus par l'élève s'améliore.

2- LE SIMULATEUR COMPOSANT - TCAD

La TCAD fait référence à une suite de logiciels permettant de simuler les processus de fabrication des

composants intégrés. L'outil de calcul de cette suite (Atlas) résout des équations différentielles issues de la

physique du composant comme celles de la diffusion ou du transport pour des géométries discrètes. Deux

logiciels principaux composent généralement cette suite d'outils dédiés à la simulation composant, à savoir,

le simulateur du procédé de fabrication et le simulateur de composant. Le premier permet de simuler les

étapes d'implantation d'ions, de dépôt, de gravure, de recuit et d'oxydation. Le second permet d'extrapoler

par simulation le comportement électrique d'un composant crée comme par exemple une diode ou un

transistor. Là aussi, le composant est représenté comme une structure maillée où chaque nœud a des

propriétés qui lui sont associés telles que le type de matériau, la concentration en dopant, etc. Ainsi, pour

chaque nœud, la concentration de porteurs, le champ électrique, etc. peuvent être calculés. Les électrodes

sont représentées par des surfaces sur lesquelles les conditions aux limites sont imposées, comme par

exemple, les tensions appliquées.

Les principaux avantages des simulateurs de composants sont tout d'abord la possibilité offerte de

visualisation de phénomènes physiques difficilement accessible et donc observable. Ensuite, ils permettent

de s'approprier de manière pédagogique les procédés de fabrication. En outre, ce sont des outils industriels

dont la connaissance peut constituer pour l'élève un atout significatif lors de sa recherche d'emploi [7].

En effet, l'évolution du profil d'une structure peut être observée durant la simulation du procédé de

fabrication. Cette fonctionnalité permet une bonne illustration du cours de conception physique des circuits

intégrés. De plus, l'outil TCAD fait acquérir aux élèves des compétences sur la fabrication des circuits

intégrés sans la nécessité d'avoir à disposition une salle blanche disposant de tous les équipements idoines.

Ainsi, avec la TCAD, les élèves peuvent expérimenter et explorer l'effet d'une modification d'un paramètre

technologique sur une structure sans coût d'équipement et de consommable. Pour finir, comme un nombre

croissant de sociétés s'affranchit de la production pour se concentrer sur la conception, la simulation

composant devient incontournable; d'où la demande croissante en ingénieurs ayant une connaissance

approfondie en TCAD.

3- EXPÉRIMENTATION

Ces TPs se déroulent dans une salle équipée de seize clients légers "Sun-Ray" pilotés par un serveur Sun

UltraSPARC-III dans lequel est installée la suite Silvaco. La série de TP est découpée en cinq sessions de

quatre heures chacune. Chaque session vise deux niveaux de compétence; la création et l'implémentation de

scripts de simulation puis l'analyse et la compréhension des résultats.

Les logiciels Silvaco utilisés par les élèves sont ATHENA le simulateur de processus de fabrication et

ATLAS le simulateur de composants. Cet enseignement arrive assez tôt dans le cursus de nos élèves. Il se

déroule juste après une série de TPs [8] dédiée à la simulation électrique illustrée par le logiciel HSPICE. De

plus, avant le début de la série, une présentation interactive du logiciel est conduite par l'enseignant. Cette

séquence préparatoire met en place les pré-requis nécessaires pour la suite des TPs. Le composant utilisé

pour cette séance préalable est une diode.

Session 1: Le simulateur de procédé ATHENA est introduit. L'élève construit, pas à pas un transistor NMOS.

Durant cette session, les profils de dopage sont analysés après chaque étape du procédé de fabrication. Cette

session se termine par l'implantation du Bore nécessaire à l'ajustement de la tension de seuil du transistor

(VT).

Session 2: Toujours avec ATHENA, la session 2 poursuit la structure réalisée à la session 1 par le dépôt du

Polysilisium et se termine à la fin de la fabrication du transistor. Comme précédemment, les profils de

dopage sont analysés après chaque étape.

Session 3: Le simulateur de composant ATLAS est présenté. Ici, l'élève doit extraire la caractéristique

électrique ID=f(VG) du transistor NMOS précédemment obtenu pour différents paramètres technologiques.

Session 4: Le simulateur mixte composant/électrique est introduit. Les caractéristiques précédentes calculées

par le simulateur de composants sont comparées aux caractéristiques similaires calculées à partir du modèle

PCM

P15

SPICE du composant. Ensuite, l'élève bâti un inverseur CMOS mixte. Cette porte logique est construite à

partir de deux transistors MOS d'origine différente: le premier est un transistor NMOS provenant de l'outil

ATHENA de Silvaco, le second est un transistor PMOS décrit au niveau électrique (SPICE).

Session 5: Dans la dernière session, un oscillateur en anneau est conçu par les élèves avec un nombre impair

d'inverseurs. Cette structure est classiquement utilisée pour contrôler le processus de fabrication des circuits

intégrés [9]. Pour minimiser les temps de calculs, un seul transistor est issu de la TCAD, les autres seront

des modèles SPICE.

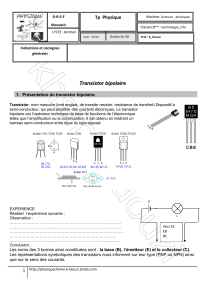

3.1 Session 1 - Définition du substrat

Le procédé de dopage est présenté aux élèves. Un puits P est créé sur un substrat initialement dopé N

(Fig. 2-a). Par l'observation de la concentration en atome de Bore, les élèves sont sensibilisés à la pertinence

de l'étape de diffusion dans le processus de dopage (Fig. 2-b). Ils ont à ajuster les paramètres de dose et

d'énergie afin d'observer le résultat sur le profil de la concentration en atome de Bore. L'objectif à atteindre

est une concentration de 10e17/cm3 en atome accepteur dans le puits P.

Pour la croissance de la couche d'oxyde de Silicium mince (SiO2), l'élève apprend à contrôler le temps et

la température d'oxydation. L'épaisseur de la couche d'oxyde est mesurée directement sur la structure (Fig.

2-c). La session se conclue par la dernière implantation de Bore assurant l'ajustement de la tension de seuil

du transistor : VT (Fig. 2-d). Les effets de la concentration seront explorés de manière électrique en session

3.

a) Silicium initialement dopé N b) puits P et diffusion

c) Oxyde mince d) Ajustement du VT

Fig. 2: Dopage du substrat et processus de diffusion avec ATHENA

3.2 Session 2 - Achèvement du transistor

Durant la première partie de la session 2, le Polysilicium est déposé puis gravé à la longueur de la grille

désirée (Fig. 3-a). Ensuite, comme le transistor élaboré est un transistor submicronique, l'élève doit

s'approprier le principe dit "Light Doped Drain" (LDD). Un dopage initial au Phosphore est opéré (Fig. 3-a).

Après quoi, le "spacer" est déposé puis gravé sur la région du drain afin de procéder au dernier dopage au

Phosphore (Fig. 3-b). Ensuite, le contact d'Aluminium est ajouté et la structure dupliquée par symétrie

verticale pour obtenir le transistor dans son ensemble (Fig. 3-c). Pour terminer, les noms des électrodes sont

ajoutés, à savoir, la grille, le drain, la source et le substrat.

PCM

P15

a) Dopage LDD b) "Spacer" et dopage du Drain c) Transistor NMOS terminé

Fig. 3: Etapes de réalisation du transistor avec ATHENA

3.3 Session 3 - Simulation TCAD-Electrique

Le simulateur électrique TCAD ATLAS est présenté aux élèves. Les réseaux de caractéristiques

classiques ID=f(VGS)VDS and ID=f(VDS)VGS sont calculés à partir du transistor élaboré lors de la précédente

session. Sur la Fig. 4, les élèves ont tracé la caractéristique ID=f(VGS)VD=0.1 pour différents paramètres

technologiques comme l'épaisseur d'oxyde mince ou la tension de seuil VT.

Transistor de départ

Variation du VT

Variation de l'épaisseur d'oxyde

Fig. 4: Simulation électrique avec ATLAS : variation de paramètres process

3.4 Session 4 - Simulation mixte TCAD-Electrique et SPICE-Electrique

La simulation mixte composant/électrique est présentée aux élèves. Le réseau de caractéristiques

ID=f(VDS)VGS obtenu par le simulateur TCAD ATLAS est comparé à celui calculé à partir du modèle SPICE

du transistor (Fig. 5-a). Ensuite, l'élève construit un inverseur mixte. C'est-à-dire, une porte élémentaire dont

les deux transistors complémentaires sont d'origine différente: le premier est le transistor NMOS conçu par

les élèves aux sessions 1 et 2 et le second est un transistor PMOS provenant d'une carte modèle SPICE issue

de la même technologie. La Fig. 5-b montre la fonction de transfert de l'inverseur créé Vout=f(Vin) obtenue

par la simulation mixte d'ATLAS.

a) ID=f(VDS)VGS b) Vout=f(Vin)

Fig. 5: Simulation électrique mixte avec ATLAS

PCM

P15

3.5 Session 5 - Simulation mixte suite

Au cours du dernier TP, les élèves ont à concevoir un oscillateur en anneau (Fig. 6-a) constitué d'un

nombre impair d'inverseurs (=3). Cette structure est classiquement utilisée pour contrôler le processus de

fabrication des "wafers". Afin de minimiser les temps de simulation, seulement un transistor provient de la

TCAD, les autres ont une description SPICE. La principale difficulté de ce genre de structure pour les

simulateurs est la nécessité de fixer les conditions initiales. Pour cela, l'élève doit composer avec la directive

de simulation .IC. Sur la Fig. 6.b, la fréquence d'oscillation obtenue peut ensuite être reliée à des paramètres

technologiques.

VDD

compact model

physical model

a) oscillateur en anneau b) signaux d'oscillation de la structure

Fig. 6: Simulation d'un oscillateur en anneau

4- CONCLUSION

Depuis plusieurs années, nous constatons un trop fort cloisonnement des enseignements de

microélectronique. Ce cloisonnement amène les élèves à percevoir une image compartimentée de la

microélectronique plutôt que de conceptualiser une vision transversale plus représentative de la réalité à

laquelle ils seront bientôt confrontés. De même, ce cloisonnement a pour effet pervers de cantonner les

enseignants dans leurs domaines de compétences. Pour cela, nous avons institué l'utilisation de la simulation

mixte afin de permettre aux élèves d'acquérir une approche plus globale des différents domaines de la

microélectronique. Mais, la principale conséquence est d'avoir obtenu, de la part d'enseignants issus de

différentes communautés, la mise en place d'objectifs pédagogiques communs. En outre, avec la simulation

mixte, les élèves mettent en œuvre un spectre plus large de compétences en simulation composant et en

simulation électrique. Nous utilisons la simulation mixte depuis maintenant deux ans. Les élèves sont très

sensibles à cette approche ainsi que les enseignants en charge des cours de conception analogique et de

physique du composant qui notent une amélioration significative de la perception des élèves dans leur

discipline respective.

6- BIBLIOGRAPHIE

[1] ModelSim : http://www.model.com/

[2] HSPICE : http://www.synopsys.com/products/mixedsignal/hspice/hspice.html

[3] Spectre : http://www.cadence.com/products/custom_ic/spectre/index.aspx

[4] Eldo : http://www.mentor.com/products/ic_nanometer_design/custom_design_simulation/eldo/

[5] Silvaco : http://www.silvaco.com/

[6] Sentaurus : http://www.synopsys.com/products/tcad/tcad.html

[7] J. Kenrow, "Integrating Professionnal TCAD Simulation Tools in Undergraduate Semiconductor Device

courses," Proceeding of the 2004 American Society for Engineering Educational Annual Conference

[8] J.-M. Gallière, "Extensive CMOS and Electrical Simulation Learning," 6th International Workshop on

Microelectronics Education, 8-9 June 2006, Stockholm, Sweden, pp. 43-46

[9] C. Landrault, "Test de Circuits et de Systèmes Intégrés," Hermes Science, Lavoisier 2004

PCM

P15

1

/

5

100%