Chapitre 7: Rangement mémoire Jeu d`instruction

Chapitre 7:

Rangement mémoire

Jeu d'instruction

M. Dubacq

IUT de Villetanneuse 20082009

2/15

Les étiquettes

> Pour programmes assembleur (pas langage machine) ;

> chaîne de caractère remplacée à l'assemblage par valeur

constante (assemblage en deux passes) ;

> Par défaut : étiquette implicite sur ligne suivante.

_main: READ _A // 00: READ 07 01

_boucle:LOAD _A // 01: LOAD 07 02

SUBI 01 // 02: SUBI 01 03

TSTN _end // 03: TSTN 06 04

STOR _A // 04: STOR 07 05

WRIT _A _boucle // 05: WRIT 07 01

_end: EJECT 0 // 06: 000000

_A: 123456 // 07: 123456

3/15

Conventions en VLTN

> Les étiquettes commencent toutes par ;

> Les étiquettes de données commencent par une majus-

cule ;

>main est déjà aectée à 00 ;

> Les commentaires sont toujours introduits par // ;

> Les étiquettes n'ont pas d'accents (comportement indé-

terminé).

4/15

La taille d'un processeur

> Diérentes tailles d'éléments en bits ;

> taille d'un mot-machine (registre entier) ;

> taille d'une instruction (registre d'instruction) ;

> taille d'une adresse (PC, pointeur) ;

> taille d'un transfert entre RAM et processeur (mot-

mémoire) ;

> Potentiellement tous diérents, souvent identiques ;

> Plus important : mot-machine.

5/15

Les registres

> Un processeur compte des registres généraux (entiers) ;

> Taille = taille d'un mot machine = taille (générale) ;

> Taille des adresses parfois diérente mais toujours dans

registre entier ;

> Souvent aussi des registres spécialisés (ottants

double) ;

> jeu d'instructions spécialisées (x87, SSE) ;

> autres registres ;

> Espace adressable = 2taille des adresses ;

> Taille = 4Gio en 32 bits, 16 Eio en 64 bits ;

> Adresse contenue dans registre entier.

6/15

Grand et petit-boutien (little/big-endian)

> Adresse 0x00000000, valeur 0x4A3B2C1D ?

> Plusieurs représentations possibles :

>Contenu 0x4A 0x3B 0x2C 0x1D

Adresse 0x03 0x02 0x01 0x00 : petit-boutien

(little endian) ;

>Contenu 0x1D 0x2C 0x3B 0x4A

Adresse 0x03 0x02 0x01 0x00 : grand-boutien

(big endian) ;

> little-endian : 6502, x86, VAX ;

> big-endian : Motorola 68000, SPARC, System/370 ;

> bi-endian : ARM, PowerPC (sauf G5), MIPS ;

> Les bi-boutiens ont un mode par défaut (big-endian pour

PowerPC, little-endian pour IA-64).

7/15

Mots, demi-mots, octets

> Une opération sur un mot (un entier) doit se faire avec

une adresse multiple de 4 ;

> Sinon, erreur dite d'alignement ;

> Il est possible de mettre dans un registre moins qu'un

mot ;

> Pour les demi-mots (16 bits), c'est LoadHalf et

StoreHalf ;

> Les adresses doivent alors être paires ;

> Pour les octets (8 bits), c'est LoadByte et StoreByte ;

> Les adresses peuvent être n'importe quoi ;

> Attention au signe. Si l'octet vaut 200, registre négatif ;

>LoadByteUnsigned pour caractères de code >128.

8/15

L'alignement dans le segment de données

> Chaque donnée prend la taille nécessaire ;

>.word (en MIPS) introduit des données sur des adresses

multiples de la taille des registres entiers, soit 4 octets ;

>.half (en MIPS) introduit des données sur des adresses

multiples de la taille des registres entiers, soit 2 octets ;

>.byte ou .ascii (en MIPS) introduit des données octet

par octet, ainsi que .space ;

> Mode d'alignement automatique des données : espace

interstitiel ;

> Possibilité de le faire manuellement par .align 4 ou

.align 2.

9/15

Différences 32/64 bits

> En 1985, 32 bits introduit car suisant pour numérotation

BD ;

> 4 Gio était 106fois la mémoire typique ;

> Maintenant, processeurs 64 bits augmente les données

et l'adressage ;

> Instructions de taille double ;

> Alignement sur taille 8 octets ;

> Perte d'espace mémoire ;

> Traitement plus rapide pour calcul massif.

10/15

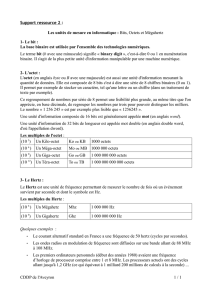

Les modèles de programmation 64 bits

Besoin de garder la compatibilité des codes sources.

En C et en C++ les types changent de taille.

Taille Taille Taille Taille Exemples

Modèle int long adresse long de

long Compilateurs

32 bits 32 32 32 64

LP64 32 64 64 64 Tous sauf...

ILP64 64 64 64 64 Exceptions...

LLP64 32 32 64 64 Microsoft...

11/15

De l'assembleur au code machine

> Opération d'assemblage faite par le programme assem-

bleur ;

> Transformation de mnémoniques en code binaire ;

> Réécriture des pseudos-instructions ;

> Utilisation du format d'instruction ;

> Transformation des étiquettes en adresses ;

> Incorporation des constantes et numéros registres aux

instructions ;

> Production de code binaire.

12/15

Les pseudos-instructions

> Instructions d'assembleur, pas de langage machine ;

> Opposées aux instructions natives ;

> Transformation en instructions natives ;

> Exemple : SET 123456 se traduit en SET 56 ;SETM

34 ;SETL 12.

> Utilisation parfois de registres spéciques ;

> Décomposition dépend parfois des valeurs constantes ;

> Exemple : constante petite (099) ou grande ;

> Remplacement automatique, mécanique.

13/15

Exemple de format d'instruction : MIPS32

Type 31 26 21 16 11 6 0

Type R op rs rt rd imm5 funct

add,sub... 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits

Type I op rs rt imm

ori,lw... 6 bits 5 bits 5 bits 16 bits

Type J op target address

j,jal... 6 bits 26 bits

> Type R : beaucoup de registres, petites constantes (pour

décalages), funct sert à compléter op ;

> Type I : Une constante sur 16 bits ;

> Type J : une grande constante sur 26 bits divisée par 4.

14/15

Exemple de format d'instruction : 486

> Taille d'instruction variable ;

> Caractéristique d'une architecture CISC ;

> Taille maximale : 16 octets.

15/15

Pénurie de codes op

> Le code op prend une partie de l'instruction ;

> Instructions peuvent être compliquées ;

> Nécessité de mettre des constantes de la taille des ins-

tructions ;

> En CISC : instructions permettant d'incrémenter tout en

tableau, de comparer deux chaînes ;

> Instructions de longueur variable !

> En RISC : instructions élémentaires ;

> Transformation d'une instruction (pseudo-instruction)

qui est pratique en une (ou plusieurs) instruction exis-

tante.

1

/

4

100%