Notes

Chapitre 3

Le MOSFET

On pr´

esente ici un r´

esum´

e de l’op´

eration du MOSFET. On parlera aussi un peu du

calcul des capacitances, ainsi que certaines m´

ethodes pour r´

esoudre les probl`

emes reli´

es

au FETs.

3.1 Op ´

eration DC

On a vu comment fonctionnait le MOSFET. L’op´

eration d´

epend de plusieurs param`

etres,

dont la tension seuil est le plus important.

3.1.1 Courant de drain

On peut identifier quatre zones d’op´

eration :

1. Zone blocage : la tension VGS < VT. Dans ce cas-ci, il n’existe qu’un tr`

es faible courant

(de l’ordre du pA au nA). Pour toutes fins pratiques, le courant ID= 0.

2. Zone lin´

eaire : la tension VDS < VGT ,VDS < VDsat, et VGS > VT. La tension entre le

grille et la source est plus grande que la tension seuil, et la tension entre le drain et

la source est faible.

3. Zone saturation : la tension VDS > VGT ,VDS < VDsat, et VGS > VT. La tension entre le

grille et la source est plus grande que la tension seuil, et la tension entre le drain et

la source est faible. Le courant produit est presque constant mˆ

eme si on augmente

la tension VDS .

4. Zone saturation de vitesse : la tension VDS > VDsat, et VGS > VT. La tension entre le

grille et la source est plus grande que la tension seuil, et la tension entre le drain

1

CHAPITRE 3. LE MOSFET

et la source est faible. Cependant, les ´

electrons ont atteint leur vitesse maximale :

saturation de vitesse.

En ´

equation, ce mod`

ele du FET, qu’on appelle le mod`

ele unifi´

eest le suivant :

1. Si VGS < VT, alors ID= 0.

2. Si VGS > VT, on calcule une tension Vmin :

Vmin = min[VDS ,VDsat,VGT ] (3.1)

o`

u

VGT =VGS −VT(3.2)

Puis on calcule le courant :

ID=k0

n

W

L VGT Vmin −V2

min

2!(1 + λVDS )(3.3)

Pour un PMOS, on remplace k0

npar k0

p, et au lieu de prendre le minimum dans l’´

equation

3.1, on prend le maximum (on obtient le mˆ

eme r´

esultat si on prend tout en valeur abso-

lue).

Rappel : La source d’un NMOS est toujours la borne la plus faible entre la source et le

drain. Pour un PMOS, c’est l’inverse : la source est toujours la borne la plus positive.

3.1.2 La tension seuil

La tension seuil VTest un autre param`

etre important du FET, qui peut varier selon le

circuit. La composante importante pour un NMOS est la tension source - substrat (VSB).

En effet, si VSB ,0, il faudra calculer une nouvelle valeur de VT.

La tension seuil est donn´

ee par l’´

equation suivante :

VT=VT0+γq2|φf|+VSB −q2|φf|(3.4)

o`

uVT0est la tension seuil lorsque VSB = 0, et γest le coefficient de l’effet du substrat.

Les param`

etres standards du processus CMOS utilis´

e dans le cours sont donn´

es dans

le tableau 3.1. Noter que ces donn´

ees sont correctes si la longueur du FET est 0.25µm. Si

le FET est plus long, la tension de saturation sera diff´

erente.

3.2 R ´

esistances

La r´

esistance d’un FET repr´

esente la r´

esistance du canal lorsqu’un courant circule.

Puisqu’on a une diff´

erence de potentiel entre le drain et la source, et qu’un courant circule,

Gabriel Cormier 2 GELE5340

CHAPITRE 3. LE MOSFET

Tableau 3.1 – Param`

etres technologique d’un processus CMOS g´

en´

erique 0.25µm.

VT0(V) γ(V0.5)VDsat (V) k0(A/V2)λ(V−1)

NMOS 0.43 0.4 0.63 115×10−60.06

PMOS -0.4 -0.4 -1.0 -30×10−6-0.1

il y a une r´

esistance. Elle est calcul´

ee de la fac¸on suivante :

RDS ≡VDS

ID

(3.5)

Cependant, lors de l’analyse d’un circuit o `

u la tension VDS varie (et donc le courant),

la r´

esistance sera variable aussi. Dans ce cas-ci, on a quand mˆ

eme besoin de calculer la

r´

esistance (pour calculer le d´

elai du circuit). Le mod`

ele de premier ordre du transistor

est celui d’un r´

esistance infinie lorsque le transistor est OFF, et d’une r´

esistance finie Ron

lorsque le transistor est ON.

Comment calculer la r´

esistance Ron ? La r´

esistance du transistor varie en fonction du

temps, est non lin´

eaire, et d´

epend du point d’op´

eration du transistor. Pour une analyse

simple, il faut une r´

esistance lin´

eaire et invariante. On va donc faire une moyenne entre

la r´

esistance `

a pleine tension (VDD ) et le point moyen de transition (VDD /2).

Ron =1

2RVdd +RVdd /2(3.6)

≈3

4

VDD

IDsat 1−7

9λVDD (3.7)

o`

uIDsat est le courant du transistor en saturation de vitesse :

IDsat =k0W

L (VDD −VT)VDsat −V2

Dsat

2!(3.8)

Remarque : La r´

esistance est inversement proportionnelle au rapport (W/L) du tran-

sistor. Si on double la largeur du transistor, par exemple, on diminue la r´

esistance de

moiti´

e.

Les r´

esistances typiques pour le processus CMOS g´

en´

erique sont Ron = 13kΩpour

un NMOS et Ron = 31kΩpour un PMOS, pour une alimentation VDD = 2.5V, pour un

transistor ayant W/L = 1. Si le transistor est plus gros, sa r´

esistance sera plus petite, et

vice-versa.

Gabriel Cormier 3 GELE5340

CHAPITRE 3. LE MOSFET

3.3 Capacitances

L’un des facteurs limitant des MOSFET sont les capacitances parasites. Ces capaci-

tances existent `

a cause de la structure physique du MOSFET : on ne peut pas les ignorer.

Elles limitent la vitesse maximale d’op´

eration des circuits int´

egr´

es.

Rappel : Une capacitance est cr´

e´

ee lorsqu’on a deux niveaux (couches) conducteurs

s´

epar´

es par un niveau di´

electrique.

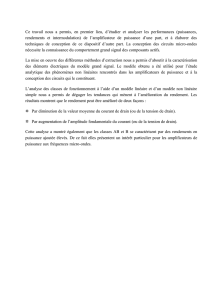

La figure 3.1 montre, de fac¸on exag´

er´

ee, o `

u se retrouvent les diff´

erentes capacitances

d’un FET.

SD

G

Substrat (B)

Jonction p-n

CSB CDB

CGB

CGS CGD

Figure 3.1 – Sch´

ema des capacitances d’un FET

On distingue alors 5 capacitances principales :

1. Capacitance de la source au substrat CSB.

2. Capacitance du drain au substrat CDB.

3. Capacitance de la grille au substrat CGB.

4. Capacitance de la grille `

a la source CGS .

5. Capacitance de la grille au drain CGD .

Ces capacitances donnent le mod`

ele de la figure 3.2.

Pour l’analyse dynamique du FET, il faudra combiner ces capacitances en trois capaci-

tances : une capacitance de grille CG, une capacitance de source CSet une capacitance de

drain CD.`

A cause de la sym´

etrie de la structure du MOSFET, la capacitance de drain et la

capacitance de source seront les mˆ

emes.

Il faut aussi mentionner que la plupart des capacitances varient selon la tension ap-

pliqu´

ee aux bornes du transistor.

Gabriel Cormier 4 GELE5340

CHAPITRE 3. LE MOSFET

S

G

D

CGD

CGS

B

CSB

CGB

CDB

Figure 3.2 – Mod`

ele des capacitances d’un FET.

3.3.1 Capacitance de grille

La capacitance de grille a deux composantes principales : une composante fixe qui

provient de la structure physique du transistor, et une capacitance qui d´

epend du mode

d’op´

eration du transistor.

Composante fixe

La composante fixe de la capacitance de grille provient du d´

ebordement entre la zone

active et la grille. Pendant la fabrication des transistors, il y a diffusion des zones actives

dessous la grille. Puisque le polysilicone de la grille et la zone active sont des conduc-

teurs, et que l’oxyde de grille est un di´

electrique, une capacitance est form´

ee. La figure

3.3 montre ce recouvrement.

Le recouvrement (overlap) a une longueur constante xdpour un processus donn´

e. La

capacitance de recouvrement est donc :

CGSO =CGDO =CoxxdW(3.9)

o`

uCox est la capacitance par unit´

e de superficie de l’oxyde de grille (en fF/µm2), xdest

la longueur du recouvrement (fixe pour un processus) et West la largeur (varie selon le

transistor). On peut combiner les ´

el´

ements fixes ensemble pour obtenir :

CGSO =CGDO =CoW(3.10)

o`

uCoest la capacitance de recouvrement par unit´

e de longueur (en fF/µm).

Gabriel Cormier 5 GELE5340

6

6

7

7

8

8

9

9

10

10

11

11

1

/

11

100%