D) Technologie de fabrication des mémoires numériques ou

D) Technologie de fabrication des mémoires numériques ou digitales:

D.1.) Organisation des mémoires à semi-conducteur.

L'ensemble des mémoires à semi-conducteur utilisent un élément de base appelé point mémoire ou

bit.

Ces points mémoire sont réalisés de différentes façon suivant le type de mémoire (SRAM,

DRAM, ROM, EPROM, EEPROM...). La réalisation d'un point mémoire entraîne une surface

plus ou moins grande suivant le type de mémoire et conditionne les capacités maximales réalisa-

bles dans chaque type de mémoire.

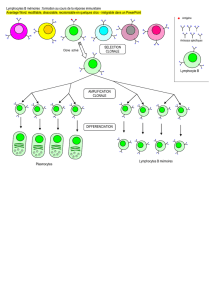

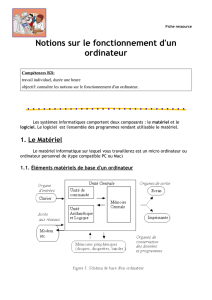

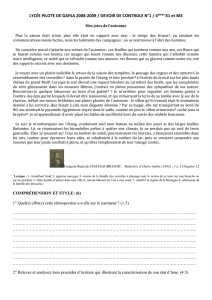

Les points mémoire sont organisés en tableau (matrice) de n ligne et m colonnes pour obtenir une

capacité mémoire importante (n * m bits).

La gestion de ces lignes et colonnes nécessite différentes fonctions ou blocs internes, en principe

au nombre de 5:

- 1) La matrice de point.

- 2) Le décodeur ligne "démultiplexeur".

- 3) Le multiplexeur colonne.

- 4) Les circuits d'entrée sortie des données (Formés d'amplificateurs trois états).

- 5) La logique de contrôle permettant le fonctionnement de l'ensemble, à partir des signaux

de sélection (/CE Chip Enable ou /CS Chip Select), /OE Output Enable, R/ W¯¯ Read / Write,

et éventuellement RAS¯¯¯¯ et CAS¯¯¯¯ pour les RAM Dynamiques).

a) Description des points mémoires élémentaires:

Dans les PROMs le point mémoire est réalisé soit par fusibles métalliques (Ni-Cr ou Ti), soit par

fusibles silicium, soit par jonctions court-circuitées. Pour les jonction court-circuitées, à la livrai-

son chaque liaison est formée de 2 jonctions en sens inverse en série (équivalent à un circuit

ouvert). La mise en avalanche d'une jonction la court-circuite (fusion => chemin conducteur).

Les points mémoires sont organisés en matrice (Voir paragraphe suivant sur l'organisation des

points mémoire).

Chaque point est à l'intersection d'une ligne et d'une colonne, afin d'obtenir un nombre de point

mémoire très important (nombre de point = produit des lignes et des colonnes).

Les Mémoires

Les mémoires suite2.lwp Page - 7 -

col 2 col 3 colonne m

Sélectiond'une ligne

Organisation matricielle des

mémoires à semi-conducteur

ligne1

ligne2

ligne n

colonne1

Décodeur ligne

A0

A1

Ai

Ai+1

Ai+2

Ai+k

Démultiplexeur

Multiplexeur

Sélection de x colonnes parmi m=x.2k

Q0 Q1 Q(x-1)

/OE

R/W

(/RAS)

(/CAS)

/OE

/CE

EN, (/RAS)

EN, (/RAS)

EN/ (/CAS)

EN/ (/CAS)

EN

1

2

3

4

5

Circuits d'entrée sortie des données

Logique

de contrôle

Matrice de points mémoire

Points mémoires

Chaque point permet d'établir un état logique 0 sur la

colonne qui lui correspond lorsque la ligne qui le

commande est sélectionnée, et que la liaison par le fusible

ou la jonction sont présent. Lorsque le fusible à été

programmé (=> détruit), la sélection de la ligne ne permet

pas au transistor d'imposer l'état bas. La résistance de tirage

de la colonne maintient alors l'état haut.

Rem: Ces mémoires existent aussi en MOS. Le principe

reste le même mais le transistor bipolaire est remplacé par

un transistor MOS. La résistance est également remplacée

par un MOS en générateur de courant.

Pour les mémoires SRAMs le point mémoire est équivalent à une bascule D (à 4 ou 6 transistors).

Le point mémoire est alors ré-inscriptible en positionnant la bascule à l'état désiré en sélectionnant

sa ligne, un circuit de lecture

écriture vient soit lire l'état de la

colonne n (ou /n) ou impose les

états des colonnes N et /n. La

bascule adopte alors cet état

logique, et le conserve même

lorsque la ligne est désélection-

née. Le point mémoire est donc

RW, et de plus statique, mais

les dimensions d'un tel point

mémoire empêchent d'obtenir

des capacités importantes dans

un espace réduit.

Rem: Les transistors Q1 et Q2

sont dit actifs, ce sont eux qui permettent le changement d'état de la bascule (FLIP FLOP), Q3 et

Q4 sont utilisés comme générateurs de courant (équivalent à une résistance de tirage ou charge).

Les transistors Q5 et Q6 permettent d'isoler le point mémoire lorsque la ligne n'est pas sélection-

née, ou au contraire de relier le point mémoire aux circuit de lecture / écriture lorsque la ligne est

sélectionnée. Dans ce cas l'information R/ W¯¯ place les circuits de sortie de la mémoire en lecture

(Read) ou écriture (Write).

Dans le cas des mémoires dynamique (DRAM) le point mémoire se limite à un transistor MOS et

un condensateur de très faible valeur.

Le principe de fonctionnement de la cellule mémoire est

assez simple : l'écriture respectivement d'un 1 ou d'un 0

consiste à charger ou à décharger le condensateur en rendant

le transistor MOS conducteur.

Une logique (amplificateur détecteur) permet de lire ou

d'écrire l'état logique de ce condensateur.

Il est possible d'obtenir une grande intégration car le point mémoire est de dimension très faible,

et il est facile de multiplier ce motif. L'inconvénient est la perte progressive de la charge des

condensateurs de mémorisation, donc perte de l'état logique mémorisé. Il est donc nécessaire de

procéder régulièrement à un rafraîchissement des points mémoires.

Les Mémoires

Les mémoires suite2.lwp Page - 8 -

Gnd

fusible

ligne

colonne

décodage ligne

+5V

Point mémoire

d'une PROM

Gnd

+5V

Col n Col /n

ligne

colonne n et /n vers circuits de lecture écriture

décodage ligne

Point mémoire

d'une SRAM

MOS

MOS MOS

MOS en

MOS en

MOS

canal N

canal N canal N

générateur

générateur

canal N

de courant

de courant

Q1 Q2

Q3 Q4

Q5 Q6

Gnd

ligne

colonne vers

décodage ligne

Point mémoire

d'une DRAM

ampli détecteur

pour lecture,

écriture et

rafraichissement

MOS

canal N

condensateur

de mémorisation

Remarque: Le condensateur est automatiquement rechargé

lors d'une lecture, par le principe de l'ampli détecteur.

Lors d'une écriture la broche de donnée (I/O) recopiera sont

état logique sur le condensateur Cn en fermant les interrup-

teurs (transistors MOS) Qad1 et Qn. Lors d'une lecture ou

d'un rafraîchissement on ferme Qn, Qad2 et Qad1. Ainsi A1

sert de comparateur et A2 d'amplificateur assurant la

recharge du condensateur.

Une fois chargé à 5 V, le condensateur a une tension

Vc qui chute à cause de sa très faible valeur, de sa

propre résistance de fuite et de la résistance non infinie

des interrupteurs 1012 Ohms.

Au bout d'un certain temps (autour de 20 ms) sa

tension a chuté de moitié et donc l'information (qui

était un 1) sera vu après ce temps comme un 0. La

donnée est perdue.

Il est donc nécessaire de rafraîchir à intervalles

réguliers les données. Si la tension Vc est supérieure à

2,5 V alors S =5V (S : tension en sortie de Qad2) et

sinon S=0V.

C'est son principe de fonctionnement qui a donné le nom à la DRAM (Dynamic RAM).

Dans les premières mémoires DRAM, il fallait par un circuit extérieur à la mémoire (circuit dédié

ou microprocesseur) faire une lecture de toutes les cases mémoires (rafraîchissement) toutes les

20 ms. Aujourd'hui les mémoires DRAM possèdent leur propre circuit de rafraîchissement

interne. Cette opération est donc devenue en partie transparente pour l'utilisateur.

De part sa structure la DRAM fournit une grande capacité mémoire et donc demande un grand

nombre de broches sur le bus d'adresse.

Ainsi pour éviter l'utilisation de boîtiers ayant un nombre de broches importants, on a décidé de

diviser par 2 le nombre de broches d'adresse. L'adresse complète est fournie en deux fois: Adresse

de ligne validée par /RAS (Row address strobe), puis adresse de colonne validée par /CAS

(column address strobe).

Les chronogrammes ci-dessous montrent la gestion en lecture et écriture des mémoires DRAMs.

Pour le cycle de lecture, le signal /WE reste à l'état haut.

Les Mémoires

Les mémoires suite2.lwp Page - 9 -

Gnd

décodage ligne

Ampli détecteur (DRAM)

ampli détecteur

point mémoire

pour lecture,

écriture et

rafraichissement

condensateur

de mémorisation

Qn

Qad1

Qad2

Cn

et colonne

A1

A2

I/O

Dans les deux cycles, l'adresse complète délivrée par le microprocesseur est fournie en deux

parties par des multiplexeurs 2 vers 1, tout en générant les signaux /RAS et /CAS. Le front

descendant de ces signaux permet à la mémoire de démultiplexer l'adresse délivrée par le micro.

Toute la logique nécessaire au fonctionnement des mémoires dynamiques (décodage,

multiplexeur, séquenceur...) Est de plus en plus souvent confiée à un circuit logique programma-

ble (FPGA). Dans le cas des ordinateurs de type PC, cette tâche est confiée à un circuit FPGA

dédié appelé "ChipSet", adapté à chaque évolution de processeur et de téchnologie de mémoires.

Avant 1990, la technologie des DRAMs n'avait pas évolué. Seule la capacité mémoire augmentait

et le temps d'accès était passé de 150 ns à 80 ns. Depuis le début des années 90, le marché des

mémoires DRAM est en pleine effervescence. En effet, voyant que le temps d'accès, de par la

technologie employée, ne pouvait pas être diminué de façon significative, les constructeurs ont

cherché à améliorer la technique d'accès aux données. Depuis 1995 , le rythme des nouvelles

technologies annoncées s'est accéléré. On compte actuellement plusieurs technologies sur le

marché: DRAM classiques, EDO, SDRAM, DDRAM, RAMBUS....

boîtier SIMM ou DIMM

Les mémoires DRAM sont principalement utilisées dans les PC sous forme de barrettes. Il existe

2 types de barrettes mémoires :

Les barrettes SIMM : à l'origine (PC386), les premières barrettes SIMM comportaient 30 broches

et devaient se placer par quatre (chaque barrette faisait 8 bits de données ) pour un bus de 32 bits.

Avec l'arrivée des PC 486 et PENTIUM, sont apparues les barrettes SIMM 72 broches. Bus de

données sur 32 bits + bus d'adresse sur 32 bits (possibilité d'adresser 4 Go) + bus de contrôle. Sur

les cartes mères Pentium il fallait placer les barrettes SIMM par paires (bus de données sur 64

bits).

Depuis 1995 et les nouvelles cartes mères à base de Pentium II, sont apparues les barrettes

DIMM 168 broches. Bus de données sur 64 bits + bus d'adresse sur 32 bits + signaux de contrôle.

Le bus de données peut être complété avec des bits supplémentaires de correction d'erreur (8 bits

de parité impaire ou code ECC Error Code Check ). Les barrettes sont alimentées en 5V ou en

3,3V.

Les Mémoires

Les mémoires suite2.lwp Page - 10 -

b) Organisation des points mémoires:

Dans tous les cas ces points sont organisés en lignes et en colonnes afin d'obtenir des capacités

importantes.

Une partie des adresses de la mémoires permettent la sélection d'une ligne unique parmi n lignes à

l'aide d'un démultiplexeur 1 parmi n. De même l'autre partie des adresses permet la sélection d'une

ou de plusieurs colonnes. Si la mémoire délivre une donnée sous forme d'octet, il faut donc un

multiplexeur de sortie fournissant 8 colonnes parmi m. Si le nombre de fils d'adresses de ce multi-

plexeur est k, il y a alors m = 2k colonnes.

Rem: 2 broches de contrôle sont présentes dans les mémoires:

/CE (ou /CS) Chip Enable ou Chip Select, permet la sélection ou la désélection du boîtier

complet.

/OE (Output Enable) permet la mise en basse ou en haute impédances des tampons de sortie, et

permet ainsi la lecture de la mémoire (Si /CE est aussi actif).

Important: Lorsque le boîtier est désélectionné (/CE inactif), il est fréquent d'obtenir une

consommation inférieure.

Il est donc intéressant d'utiliser cette broche pour la commande par le décodage d'adresse, afin de

réduire la consommation. Malheureusement le temps d'accès aux données est alors souvent

supérieur si la commande est réalisée par la broche /CE, que si la commande est effectuée par

/OE.

Les Mémoires

Les mémoires suite2.lwp Page - 11 -

Gnd

fusible

Gnd

fusible

Gnd

fusible

Gnd

fusible

Gnd

fusible

Gnd

Gnd

fusible

Gnd

fusible

Gnd

ligne1

ligne2

ligne n

colonne1 colonne2 colonne mdécodage ligne

Sélectiond'une ligne

+5V +5V +5V

Organisation matricielle des

points mémoire d'une PROM

A0

A1

Ai

Ai+1

Ai+2

Ai+k

Démultiplexeur

Multiplexeur

Sélection de x colonnes parmi m=x.2 k

Q0 Q1 Q(x-1)

/OE

/OE

/CE

EN

EN

Fusible détruit ou défaut de

métallisation dû au masque

6

6

7

7

8

8

1

/

8

100%