Intégration et étude de cellules STT

Intégration et étude de cellules STT-MRAM pour des applications haute vitesse

et ultra-basse consommation

Contact : Ioan-Lucian PREJBEANU DSM/INAC/SPINTEC [email protected] 04 38 78 91 43

Stage pouvant se poursuivre en thèse : Oui

Résumé :

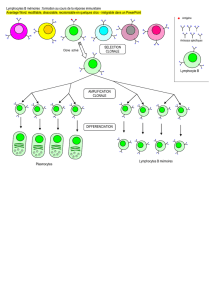

Afin de surmonter les limites en termes de miniaturisation et consommation des circuits logiques actuels, l'industrie des semi-conducteurs intègre de

plus en plus de composants mémoires non-volatiles à l'intérieur de ces puces. Parmi celles-ci, les mémoires magnétiques STT-MRAM sont les plus

prometteuses. L'attractivité de cette technologie innovante vient de par sa très haute vitesse de programmation (GHz) et son endurance infinie. Les

applications envisagées sont les intégrations de type « memory-in-logic » permettant des applications ultra basse consommation à démarrage

instantané « instant-on ». Cependant d'importants challenges technologiques pour la réalisation de ces structures doivent être relevés notamment en

termes d'intégration et de caractérisation avec la logique.

Sujet détaillé :

L'objectif de ce stage est de réaliser et d'étudier des mémoires STT-MRAM intégrés sur des transistors.

Le travail s'articulera ainsi autour de 2 axes :

- (1) Réalisation et suivi de fabrication de mémoires STT-MRAM intégrées sur transistor. Avec l'aide de l'expertise du Laboratoire Composants

Mémoires et les moyens de fabrication des salles blanches du LETI, le candidat réalisera les dispositifs. Au sein de l'équipe mémoire, le candidat

proposera des optimisations en étroite collaboration avec les experts technologiques du LETI et SPINTEC.

- (2) Caractérisation électriques des cellules mémoires STT-MRAM et structures associés. Développement de tests et de procédures adaptés à ces

cellules. La vitesse de commutation, la consommation ainsi que la fiabilité seront étudiées sur des structures de type 1R et 1T-1R.

Unité d'accueil CEA-LETI - DRT/DCOS/SCME/LCM

Contacts : Etienne Nowak - LETI ([email protected])

Ricardo Sousa ([email protected])

Lucian Prejbeanu ([email protected]),

Compétences requises :

microélectronique, physique du solide

1

/

1

100%