Les Mémoires

Mr COTTET

Les Mémoires

Fonction mémorisation

A) Classification des mémoires:

On distingue deux grand type de mémoire:

1) Les mémoires de type analogique (Bandes magnétiques, disques vinyles). Elles permettent

l'enregistrement et la restitution de signaux analogiques avec de nombreuses contraintes liées au type

de support de mémorisation (Faible rapport signal sur bruit ’40 à 70 dB max., bande passante limitée

tant dans les basses, que dans les hautes fréquences. Mauvaise fiabilité à long terme. Transmission,

mémorisation et restitution avec perte de qualité..). L'avantage principal réside dans les capacités

importantes de mémorisation dans le cas des bandes magnétiques.

2) Les mémoires de type numériques ou digitales (Utilisées principalement dans les systèmes de

traitement, d'enregistrement, de restitution ou de transmission de données numériques: Ordinateurs,

appareils photos numériques, camescopes numériques, répondeurs enregistreurs numériques,

téléphones portables, cartes téléphoniques ou cartes à puces diverses...).

B) Définition des grandeurs caractérisant les mémoires numériques ou digitales:

1) La Capacité

Elle représente la quantité d'information pouvant être stockée dans la mémoire. Elle est souvent

exprimée en kilo bits. Elle caractérise le nombre d'éléments, bits, octets ou mots mémorisables par

un circuit mémoire.

Elle est souvent exprimée en clair et dans ce cas plutôt en kilo bits :

Ex: Pour une mémoire UVPROM AM27C256.

256 Kilo bit (32 768 x 8 Bit) CMOS EPROM

AM est le préfixe du fabriquant (Advanced Micro Devices ).

Le préfixe 27 représente une mémoire de type UVPROM (ou EPROM), La

lettre C indique la technologie CMOS. Ensuite 256 représente la capacité en

kilo bits.

Pour cette mémoire les mots sont organisés en octets (Voir DQ0 à DQ7 sur

le brochage de la mémoire voir page suivante) donc 8 Bits pour former un

octet.

Les Mémoires

Les mémoires Page - 1 -

C'est un circuit qui peut mémoriser 32k mots de 8 bits (octet), sa

capacité est donc de 256 kilo Bits ou 32 kilo Octets.

256 kilo bits

8=32kOctets

Rapport entre le nombre de ligne d'adresses et la capacité.

La mémoire AM27C256 est organisée sous forme d'octets et comporte

15 lignes d'adresses (A0 à A14, voir le brochage de la mémoire) = 215 =

25 * 210 = 32 * 1024 mots mémoire de 8 bits de données.

Cette mémoire de 32k Octets a donc une capacité de 32 x 1024 x 8 =

256 x 1024 bits.

256 k bits ou 32 k Octets.

Attention:

Les barrettes ou modules mémoire sont souvent organisées sur plus de 8 bits et manipulent des

mots de 16, 32 bits ou plus.

Si l'on prend un module mémoire (barrette) de 128 kilo

mots de 16 bits (128 k words) = 128 x 1024 x 16 bits , c'est

un module de capacité 128 kilo mots de 16 bits, soit 128 x

16 = 2048 kilo bits ou 2 méga bits.

1k = 1024; 1 Méga = 1024K

Par contre le nombre de fils d'adresses nécessaire permet d'adresser 128 kilo mots (chaque adresse

correspond à un élément de la mémoire, soit ici un mot de 16 bits). Il faut donc n fils d'adresses

tels que 2n = 128 k = 27 x 210 = 217 soit 17 fils de A0 à A16.

2) Le mode d'accès.

Les mémoires sont divisées en deux catégories:

2.1) Les mémoires à accès aléatoires, ou il est possible d'accéder à une information quelconque en

un temps constant. C'est le cas des mémoire en circuit intégrés à accès parallèle.

2.2) Les mémoires à accès séquentiel, ou le temps dépend de la position de l'information. C'est le

cas des mémoires de stockage de masse (bande), mais aussi de nombreuses mémoires à accès

série (registres à décalage de type LIFO = Last In First OUT, ou de type FIFO = First IN First

OUT, les C.C.D. "Charge Coupled Device", mémoire à bulles magnétiques...).

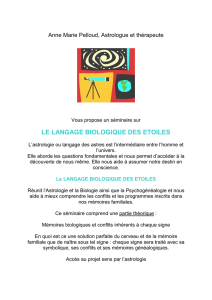

3) Les temps d'accès et temps de cycle.

3.1) Temps d'accès:

C'est le temps nécessaire pour effectuer une opération de lecture ou d'écriture (d'un bit ou mot..).

Ce temps peut être court pour les mémoires à accès aléatoire (Ex: 100 ns), mais est souvent très

important pour celles à accès séquentiel (plusieurs dizaine de milliseconde pour les mémoires en

circuit intégré à accès série, mais plusieurs secondes à plusieurs minutes pour des unité de bandes

magnétiques).

3.2) Temps de cycle:

C'est la durée minimale séparant 2

accès consécutifs à la mémoire

(en lecture ou en écriture).

Rem: Certaines mémoires

peuvent avoir un temps d'accès

important mais un temps de cycle

Les Mémoires

Les mémoires Page - 2 -

Données

Adresse (n) Adresse (n+1)

T accès

T cycle

Les informations peuvent changer

Informations stables

faible. C'est le cas des bandes magnétiques car il faut parfois plusieurs minutes pour placer la

bande à l'endroit désiré (= temps d'accès). Ensuite les données sont lues ou écrites les unes à la

suites des autres et permet d'obtenir des débits de plusieurs MO secondes. Le temps de cycle est

alors inférieur à la µs.

3.3) Temps de cycle lecture écriture:

C'est la durée minimale d'un cycle comportant une lecture suivie d'une écriture. Ce temps diffère

également en fonction des mémoires. Il est parfois même impossible de spécifier ce temps, lorsque

l'écriture et la lecture ne peuvent pas se suivre directement (dispositif différent pour l'écriture dans

le cas de programmateur, ou lecture impossible pendant l'écriture pour les graveurs...)

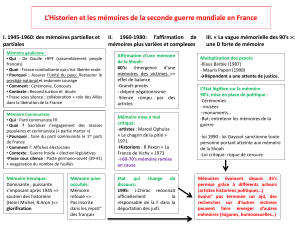

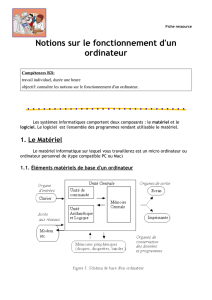

C) Classification des mémoires numériques à semi-conducteur:

C.1) Les ROMs : Mémoire Morte, la ROM (Read Only Memory)

C'est une mémoire à lecture seule (Read Only Memory), l’écriture nécessite un programmateur ou une

procédure plus longue que pour les RAMs. Les informations qu'elle contient sont conservées en perma-

nence, même lors d’une coupure d’alimentation.

1.1) ROM (Read Only Memory)

Masque de fabrication à :

- diodes disposées sur un réseau de lignes et de colonnes.

- ou à transistors dont sont effectuées des coupures à leurs bases.

1.2) PROM à fusibles ou FPROM (Programmable Read Only Memory ou Fuse PROM)

Réalisée à partir de transistors bipolaires dont leurs liaisons entre l'émetteur et la colonne sont effec-

tuées par l'intermédiaire d'un fusible.

1.3) EPROM (Erasable Programmable Read Only Memory)

Elles possèdent les avantages de la PROM avec un plus, qui est l'effacement des données par l'utilisa-

teur.

Les Mémoires

Les mémoires Page - 3 -

Les mémoires mortes (ROM : Read Only Memory)

MEMOIRES

MORTES

ROM

FPROM

UVPROM EEPROM EEPROM

FLASH

EPROM OTP

PROM

Le terme EPROM correspond à un ensemble de composants. Abusivement on utilise ce terme pour les

UVPROM.

1.4) OTP MEMORY (One Time Programmable MEMORY)

- programmable une seule fois à l’aide d’un programmateur (Rem : On utilise souvent le terme PROM

pour l’ensemble (PROM, FPROM, OTP).

- mémoire en technologie MOS

Souvent c’est une UVEPROM mais en boîtier plastique sans fenêtre de quartz (Le coût en est ainsi

réduit). Elles remplacent donc les UVPROMs lors d’une production en grande série après avoir

développé une pré série avec des UVPROMs. Elles sont compatibles broches à broches avec les

UVPROMs.

1.5) UVPROM (EPROM effaçable par une exposition aux ultraviolet U.V.)

Ce type de mémoire est placée dans un boîtier céramique avec fenêtre de quartz

(windowed)

- effaçable aux U.V.

- effacement de la mémoire toute entière

- constituée de transistors MOS dont la grille est isolée

- 10 à 20 minutes pour effacer sous une source d'U.V. (effaceur)

- haute tension de programmation environ 12,5 à 25 volts

- temps de programmation relativement long (environ 50 ms max. par octet, Ex : pour une 27256 soit

32 K Octet x 8 bits, il faut 32*1024*50ms = 1638s = 27 mn). Les constructeurs de mémoires dévelop-

pent des algorithmes de programmation rapide afin de diminuer le temps de programmation.

1.6) EEPROM ou E2PROM (Erasable Electricaly PROM)

- effaçable électriquement

- coût de fabrication élevé entraînant des capacité réduites

- effacement adresse par adresse possible ou par bloc

- comme une mémoire flash mais avec un temps d’écriture beaucoup plus long (>15mS).

Il existe des mémoires EEPROM à accès parallèle et des mémoires EEPROM à accès série. à Pour celle

à accès parallèle, les données entrent et sortent sous la forme d’un octet.

Pour celles à accès série, les données entrent et sortent en série en commençant par le bit de poids fort

des octets. La liaison série utilisée est de type synchrone (SPI ou I2C). Dans ce cas, ces mémoires sont

intéressantes par leur faible encombrement (boîtier DIP8), puisque l’adresse et la donnée sont transmise

sous forme série. Toutefois le temps d’accès au données est alors relativement long.

1.7) EPROM FLASH

- effaçable électriquement

- écriture plus rapide que les EEPROM

- mais effacement de toute la capacité de la mémoire en un coup.

- prix plus faible que les EEPROM

- haute tension de programmation environ 12 volts

Les Mémoires

Les mémoires Page - 4 -

C.II) Les RAMs : Mémoire Vive, la RAM (Random Access Memory)

Les mémoires RAM sont volatiles et à accès direct (Accès aléatoire en lecture ou écriture).

Dans cette catégorie de mémoires on trouve :

Les mémoires RAM statiques (SRAM) dans lesquelles les informations sont mémorisées par une

bascule de type D et conservées tant que l'alimentation est présente (mémoire volatile), elles sont réali-

sées en technologie MOS ou bipolaire.

Les mémoires RAM dynamiques (DRAM) qui utilisent un condensateur comme cellule mémoire (un

bit mémorisé) de l'information. Cette information tend à se dégrader à cause des courants de fuites, ce

qui nécessite un rafraîchissement périodique.

C'est l'espace de travail pour les ordinateurs. C'est là que se recopient le système d'exploitation et les

applications (programmes), stockés sur le disque dur, et ou sont transformés vos documents avant

sauvegarde sur une mémoire de masse.

Pour les systèmes micro industriels c’est l’emplacement des données appelées variables. Ces données

peuvent correspondre à des variables globales ou locales du programme, ou à des données de transmis-

sion ou de traitement (acquisition, valeurs de sortie).

Avantages : Ces mémoires sont rapides, voir même très rapide pour les SRAM = RAM statique), ou

elles peuvent atteindre de grandes capacité dans le cas des DRAM = RAM dynamiques.

Inconvénient : Elles sont volatiles. Lorsque l’alimentation est coupée, les informations qu'elles contien-

nent disparaissent.

Cas particuliers et applications :

1) SRAM = Static RAM. Elles sont très rapides, mais de capacité réduite et de coût élevé. (Ex : qq

100KO avec 50 ns de temps d’accès). Elles sont souvent facile à mettre en œuvre d’un point de vue

connexion.

Application : Mémoire d’oscilloscope numérique, mémoire cache d’ordinateur

2) DRAM = Dynamic RAM. Elles permettent d’obtenir des

capacités importantes (sous forme de modules mémoires appelés

barrettes). A une date donnée, leur capacité est souvent plus de

1000 fois la capacité des SRAMs, mais pour des temps d’accès

parfois 10 à 20 fois supérieurs.

Le système micro doit être conçu pour assurer le rafraîchissement de ces mémoires de manière

régulière. Cette tâche est maintenant facilité, car les composants nécessaires au rafraîchissement sont

souvent intégrés aux modules mémoires (compteurs d’adresses). Toutefois elles sont difficile à gérées, il

est souvent préférable de les associer à un circuit spécialisé de gestion assurant le décodage et les

opérations de multiplexage des adresses etc… (On utilise des circuits logiques programmables, CPLDs,

FPGAs …).

3) NOVRAM = (Non volatile RAM).

Mémoire de type SRAM associée à une pile de sauvegarde, ou système de transfert vers une mémoire

morte de type FLASH.

Leur coût à capacité égale est supérieur aux SRAMs. Elles sont donc limitées aux applications micro

contrôleurs industriels ou il est indispensable de ne pas perdre les données.

Les Mémoires

Les mémoires Page - 5 -

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

1

/

14

100%