PIA : Processeurs et Implantation d`Algorithmes

Département Signal et Télécommunication Année Scolaire 2007/2008

5B ISE SIS 1/23 TP PIA

5BE/5BS : Travaux Pratiques

PIA : Processeurs et Implantation

d’Algorithmes

Département Signal et Télécommunication Année Scolaire 2007/2008

5B ISE SIS 2/23 TP PIA

Le microprocesseur TMS320C50

Organisation générale

D'un point de vue physique, le C50 est doté d'une mémoire interne et peut être équipé de mémoire externe.

Chacun de ces espaces est lui-même séparable en quatre espaces fonctionnels :

– mémoire de programme,

– mémoire de données locale,

– mémoire de données globale (uniquement en mémoire externe),

– ports d’entrée/sortie.

La mémoire que le C50 est capable d’adresser est composée de :

– 64 K mots de 16 bits de mémoire de programme,

– 64 K mots de 16 bits de mémoire de données configurables en :

– mémoire de données locales,

– mémoire de données globales : zone mémoire permettant de partager des données entre plusieurs

processeurs.

– 64 K ports d’entrée/sortie (Input/Output).

La mémoire interne

L’utilisation de la mémoire interne, intéressante du point de vue temps d’accès, permet de travailler même en

l'absence de mémoire externe. Le TMS320C50 dispose de 10 K mots de RAM et de 2 K mots de ROM

organisés de la façon suivante :

– 2 K mots de 16 bits de ROM de démarrage, éventuellement activée à l’initialisation pour accéder à une

REPROM externe. Si cette possibilité n'est pas utilisée, une ROM externe de 32 K mots est accessible

directement entre 0 et 7FFH.

– 9 K mots de 16 bits de mémoire RAM programme ou données en simple accès,

– 1056 mots de 16 bits de RAM de données double accès (une lecture/écriture par cycle).

Dans la configuration utilisée dans le kit DSK, le processeur travaille en mode microprocesseur (la broche

MP MC est à 1), c'est-à-dire utilisant la ROM externe comme ROM programme.

La ROM interne

La ROM interne contient un programme d’initialisation (boot loader) qui permet, lors de la mise sous tension du

système d’initialiser le processeur et son environnement, et de transférer un programme utilisateur vers la

mémoire RAM du DSP. La ROM interne est située de 0000H à 07FFH.

Département Signal et Télécommunication Année Scolaire 2007/2008

5B ISE SIS 3/23 TP PIA

La RAM simple accès

Elle est formée de quatre blocs de 2 K mots et d’un bloc de 1 K mots. Elle nécessite un cycle du processeur

pour une opération de lecture ou d'écriture. Deux bits permettent la configuration de cette RAM simple accès ;

les bits OVLY et RAM du registre PMST :

RAM

0 1

OVLY 0 SARAM invalide SARAM Programme

1 SARAM Donnée SARAM Programme et Donnée

Figure 1 : Configuration de la SARAM

Les 9 K mots de RAM simple accès sont positionnés à l’adresse 800h dans la configuration mémoire de

programme ou mémoire de données.

La RAM double accès

La taille de cette mémoire est de 1056 mots de 16 bits. Comme son nom l’indique, le processeur peut accéder

deux fois à cette mémoire en un seul cycle : une fois en écriture et une fois en lecture. Cette mémoire permet

trois configurations différentes.

Les configurations

Les configurations passent, entre autres, par l'utilisation des registres ST0 (registre d'état 0), ST1 (registre

d'état 1), PMST (Processor Mode Status Register) et CBCR (Circular Buffer Control Register).

Configuration mémoire "données"

– Bloc B0 de 512 mots entre 100H et 2FFH en mémoire de données locale ou FE00H à FFFFH en espace

programme (configurable en fonction du bit CNF qui est à 0 lors du Reset indiquant que B0 est en mémoire

de données).

– Bloc B1 de 512 mots entre 300H et 4FFH en mémoire de données locale.

– Bloc B2 de 32 mots entre 60H et 7FH en mémoire de données locale.

Configuration mémoire programme - mode microprocesseur (bit MP MC=1)

Seul le bloc B0 est accessible aux adresses FE00h à FFFFh.

Département Signal et Télécommunication Année Scolaire 2007/2008

5B ISE SIS 4/23 TP PIA

Configuration mémoire programme - mode microcontrôleur (bit MP MC =0)

Seul le bloc B0 est accessible aux adresses FE00h à FFFFh.

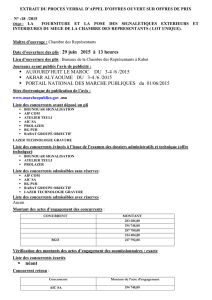

CNF RAM MP MC SARAM DARAM ROM Externe

0 0 0 0h-07FFh 0800h-FFFFh

0 0 1 0h-FFFFh

0 1 0 0800h-2BFFh 0h-07FFh 2C00h-FFFFh

0 1 1 0800h-2BFFh 0h-07FFh

2C00h-FFFFh

1 0 0 FE00h-FFFFh 0h-07FFh 0800h-FDFFh

1 0 1 FE00h-FFFFh 0h-FDFFh

1 1 0 0800h-2BFFh FE00h-FFFFh 0h-07FFh 2C00h-FDFFh

1 1 1 0800h-2BFFh FE00h-FFFFh 0h-07FFh

2C00h-FDFFh

Figure 2 : Configurations et cartographies de la mémoire programme

Configuration de la mémoire

– Emplacement des bits CNF, OVLY, RAM, MP MC, etc.

Les bits OVLY, RAM, MP MC se trouvent dans le registre PMST (Processor Mode Status Register) :

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

bit

0

IPTR

0

0

0

AVIS

0

OVLY

RAM

MP

MC

NDX

TRM

BRAF

Figure 3 : Registre PMST

Le bit CNF se trouve, quant à lui, dans le registre ST1 (Status Register 1) :

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

bit

0

ARB

CNF

TC

SXM

C

1

1

HM

1

XF

1

1

PM

Figure 4 : Registre ST1

– Quelques instructions de l’assembleur du TMS320C50

OPL : cette instruction nécessite un ou deux opérandes. Si le premier opérande est un entier long, OPL

effectue un OU LOGIQUE entre le premier et le second opérande. Le résultat est réécrit dans le second

opérande. S’il n’y a qu’un seul opérande, la même opération a lieu entre l’unique opérande et le registre

DBMR (Dynamic Bit Manipulation Register).

SETC : l’opérande est l’un des bits des registres de contrôle ST0 ou ST1 qui est mis à 1.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

bit

0

ARP

OV

OVM

1

INTM

PM

Figure 5 : Registre ST0

CLRC : l’opérande est l’un des bits des registres de contrôle ST0 ou ST1 qui est mis à 0.

Département Signal et Télécommunication Année Scolaire 2007/2008

5B ISE SIS 5/23 TP PIA

Exemples :

OPL #010h, PMST 010h = 16 = 24 = 010000b : le cinquième bit de PMST (bit RAM) est mis à 1. Cela

positionne donc la RAM simple accès dans l’espace mémoire programme.

OPL #8, PMST 8 = 23 = 01000b : le quatrième bit de PMST (bit MP MC) est mis à 1. Cela valide

la mémoire programme externe à l’adresse 0.

SETC CNF CNF = 1 : validation de la mémoire double accès.

CLRC CNF CNF = 0 : invalidation de la mémoire double accès.

Gestion de la mémoire globale

La mémoire globale fait partie de la mémoire externe que le TMS320C50 est capable d’adresser. L’adjectif

globale provient du fait que c’est une zone mémoire à laquelle plusieurs processeurs peuvent accéder. Un

arbitrage gère l’accès à cette mémoire. Le registre GREG permet de configurer la taille ainsi que l’adressage

de la mémoire globale comme le montre le tableau ci-dessous.

Contenu binaire

de GREG Adresses

mémoire locale Taille mémoire

locale Adresses mémoire

globale Taille mémoire

globale

000000xx 0h-0FFFFh 65 536

0

10000000 0h-07FFFh 32 768 08000h-0FFFFh 32 768

11000000 0h-0BFFFh 49 152 0C000h-0FFFFh 16 384

11100000 0h-0DFFFh 57 344 0E000h-0FFFFh 8 192

11110000 0h-0EFFFh 61 440 0F000h-0FFFFh 4 096

11111000 0h-0F7FFh 63 488 0F800h-0FFFFh 2 048

11111100 0h-0FBFFh 64 512 0FC00h-0FFFFh 1 024

11111110 0h-0FDFFh 65 024 0FE00h-0FFFFh 512

11111111 0h-0FEFFh 65 280 0FF00h-0FFFFh 256

Figure 6 : Configuration de la mémoire globale

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

1

/

23

100%

![Cours AIC.ppt [Lecture seule]](http://s1.studylibfr.com/store/data/004201692_1-ddcecffcc1da320a89fa5895817e32e1-300x300.png)