Complétude fonctionnelle Circuits combinatoires Comparateurs n-bits

Licence Informatique S3

Architecture des ordinateurs

Aix Marseille Universit´e 2013-2014

http://pageperso.lif.univ-mrs.fr/~peter.niebert/archi2013.php

TD num´ero 2 : Circuits combinatoires

Des exercises marqu´es avec (∗) sont des devoirs maison. Votre note contrˆole continu d´epend

entre autre de ce que vous rendez sur ces exercices.

Compl´etude fonctionnelle

Exercice 1 Montrer :

– Toute fonction bool´eenne peut ˆetre calcul´ee par un circuit n’utilisant que des portes NAND,

ou que des portes NOR.

– La fonction ORne peut pas ˆetre calcul´e par un circuit n’utilsant que des portes XOR.

Circuits combinatoires

Exercice 2 [afficheur 7 segments] (*) Nous discutons le s´egment s7dans le TD, les autres segments

sont devoir maison .

s1

s6

s5

s7

s2

s3

s4

Donner pour chacune des fonctions s1, s2, s3, s4, s5, s6, s7une expression en forme normale

disjontive la plus simple possible pour une entr´ee 4bits (x3x2x1x0)2et des valeurs d´ecimales.

Indication : utiliser des tables de Karnaugh et optimiser par rapport aux combinaisons d’entr´ees

non-sp´ecifi´ees (valeurs de 10 et plus). Puis, donner un circuit complet pour un d´ecodeur 4bit -

7segments, notamment en profitant de la possibilit´e de partage.

Comparateurs n-bits

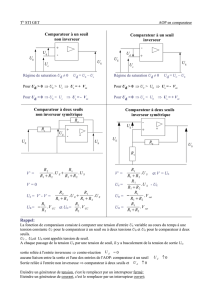

On souhaite r´ealiser un comparateur pour des nombres de nbits avec les op´erations <(stric-

tement plus petit) et ≤(plus petit). Nous allons proc´eder de deux fa¸cons diff´erentes et ´etudier

chacune des deux solutions en terme de nombre de portes logiques utilis´ees et de temps de calcul.

Exercice 3 (Comparateur associatif)

Question 3.1 Dessiner deux circuits Comp<et Comp≤ayant tous les deux 2 entr´ees aet bet

une sortie svalant 1 si respectivement a<bet a≤b.

On utilise un comparateur par paire de bits, qui dispose de plus de deux entr´ees valant les

r´esultats de comparaison pour les bits pr´ec´edents dans les deux nombres. On retrouve `a la figure

1 `a gauche un des ces comparateurs associatifs et sur la droite, leur assemblage pour obtenir un

comparateur 3 bits.

Chaque comparateur associatif utilise le principe suivant :

0

a1a2a3

b1b2b3

a

b

<

<=

<

<=

in

in

<out

<=out 1

Figure 1 –

–(anan−1. . . a2a1)2<(bnbn−1. . . b2b1)2ssi

an< bnou an=bnet (an−1. . . a2a1)2<(bn−1. . . b2b1)

–(anan−1. . . a2a1)2≤(bnbn−1. . . b2b1)2si et seulement si

an< bnou an=bnet (an−1. . . a2a1)2≤(bn−1. . . b2b1)

Question 3.2 Selon ce principe, d´efinir un circuit COMB permettant de construire un compara-

teur associatif en combinant des entr´ees <in et ≤in et les r´esultats des circuits Comp<et Comp≤.

Question 3.3 Pour le circuit obtenu, donner, en fonction de n, le nombre de portes logiques

n´ecessaires `a la r´ealisation d’un comparateur de nombres de nbits comme celui d´ecrit figure 1.

Question 3.4 Pour le circuit obtenu, calculer, en fonction de net de tle temps de passage d’une

porte logique pour les signaux, au bout de combien de temps les r´esultats de la comparaison sont

disponibles sur la sortie.

Exercice 4 (Comparateur r´ecursif) Etudions maintenant une autre mani`ere de r´ealiser un

comparateur nbits ; nous supposons ici que nest une puissance de 2, ie ∃d∈N,n= 2d.

Question 4.1 Montrer comment les deux relations d’ordre <et ≤entre (anan−1. . . a n

2+1)2et

(bnbn−1. . . b n

2+1)2et entre (an

2an

2−1. . . a1)2et (bn

2bn

2−1. . . b1)2permettent de calculer les relations

d’ordre entre (anan−1. . . a2a1)2et (bnbn−1. . . b2b1)2.

Question 4.2 R´ealiser un comparateur pour nbits `a l’aide de 2 comparateurs pour n

2bits (dont

vous supposez disposer) et le circuit COMB obtenu pr´ec´edemment.

On peut de mani`ere r´ecursive appliquer le mˆeme principe et construire chacun des comparateurs

pour n

2bits avec 2 comparateurs pour n

4bits qui eux-mˆeme peuvent se construire avec .....

Question 4.3 D´ecrire comment selon ce principe, on peut obtenir un comparateur pour nbits en

utilisant uniquement des circuits Comp<, Comp≤et COMB .

Question 4.4 Calculer le nombre de circuits Comp<, Comp≤et COMB et donc, le nombres de

portes logiques utilis´e(e)s dans votre comparateur r´ecursif pour nbits.

NB : le terme g´en´eral de la suite un=2un

2+csi n > 1

ksi n= 1 est un=n∗k+ (n−1) ∗c.

Question 4.5 Calculer, en fonction de net de tle temps de passage d’une porte logique , au bout

de combien de temps les r´esultats de la comparaison pour nbits sont disponibles sur la sortie.

Exercice 5 Concevoir un circuit pour la multiplication pour deux nombres `a deux bits avec un

r´esultat `a 4 bits. Vous pouvez utiliser comme composants des circuits d’addition.

2

1

/

2

100%