Conversion analogique-numérique et numérique

1

Module d’Electronique

3

ème

partie : Conversion de données

Fabrice Sincère (version 3.0.1)

http://pagesperso-orange.fr/fabrice.sincere

2

Introduction

• 2 catégories de circuits électroniques :

– circuits analogiques (∩)

– circuits numériques (#)

3

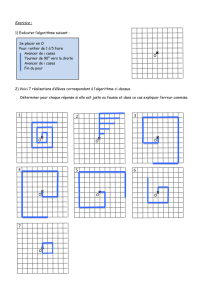

• Le convertisseur analogique/numérique permet de

communiquer d’un système analogique vers un système

numérique :

– Fig. 1a

– Exemples

• Capteur de son (microphone) ∩ → Carte-son

→Ordinateur #

• Capteur de température ∩

→Carte d’acquisition →Ordinateur #

an-1

a1

a0

entrée

uE

111

1 1 1

1 1 1 1

0 0

0 0 0

0 0

1

horloge

tension de

référence

0

0

0

t t

4

• Le convertisseur numérique/analogique permet de

communiquer d’un système numérique vers un système

analogique :

– Fig. 1b

– Exemples

• Ordinateur # → Carte-son →amplificateur et

haut-parleurs ∩

• CD # → Lecteur CD →amplificateur et haut-

parleurs ∩

an-1

a1

a0

sortie

uS

tension de

référence

111

1 1 1

1 1 1 1

0 0

0 0 0

0 0

10

0

0

tt

5

Chapitre 1

Convertisseur numérique/analogique

(CNA)

Digital-to-Analog Converter (DAC)

1-1- Définitions

• Un CNA convertit un nombre binaire en une tension (ou

un courant) qui lui est proportionnel.

– L’entrée est numérique (n bits) : N = (a

n-1

…a

1

a

0

)

2

n est la résolution numérique

N

min

= (0…00)

2

= 0

N

max

– 1 = (1…11)

2

= 2

n

- 1

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

1

/

39

100%

![III - 1 - Structure de [2-NH2-5-Cl-C5H3NH]H2PO4](http://s1.studylibfr.com/store/data/001350928_1-6336ead36171de9b56ffcacd7d3acd1d-300x300.png)